# DISEÑO E IMPLEMENTACIÓN DEL PROTOTIPO DE UN OSCILOSCOPIO DIGITAL BASADO EN EL SISTEMA EMBEBIDO MINI2440

CESAR DAVID REVELO APRAEZ JOSE LUIS ORDOÑEZ REVELO

UNIVERSIDAD DE NARIÑO FACULTAD DE INGENIERÍA INGENIERÍA ELECTRÓNICA SAN JUAN DE PASTO 2012

# DISEÑO E IMPLEMENTACIÓN DEL PROTOTIPO DE UN OSCILOSCOPIO DIGITAL BASADO EN EL SISTEMA EMBEBIDO MINI2440

# CESAR DAVID REVELO APRAEZ JOSE LUIS ORDOÑEZ REVELO

Trabajo de grado para optar al título de Ingeniero Electrónico

DIRECTOR

DARÍO FERNANDO FAJARDO

INGENIERO ELECTRÓNICO

ASESOR

MARIO FERNANDO JOJOA ACOSTA

INGENIERO ELECTRÓNICO

UNIVERSIDAD DE NARIÑO FACULTAD DE INGENIERÍA INGENIERÍA ELECTRÓNICA SAN JUAN DE PASTO 2012

# Nota de Responsabilidad "La Universidad de Nariño no se hace responsable por las opiniones o resultados obtenidos en el presente trabajo y para su publicación priman las normas sobre el derecho de autor". Acuerdo 1. Artículo 324. Octubre 11 de 1966. Emanado del honorable Consejo Directivo de la Universidad de Nariño.

| Nota de aceptación                      |

|-----------------------------------------|

|                                         |

|                                         |

|                                         |

|                                         |

|                                         |

|                                         |

| Firma del presidente del Jurado         |

| Firma del jurado                        |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

| Firma del jurado                        |

A Dios, por habernos permitido culminar con éxito la realización de este proyecto, y a nuestros padres por brindarnos la oportunidad de hacer realidad este sueño compartido, gracias por su incondicional apoyo y formidable ejemplo.

### **AGRADECIMIENTOS**

A todas las personas que participaron e hicieron posible la realización de este proyecto, muchas gracias por su apoyo y enseñanza:

Darío Fernando Fajardo, Director Mario Fernando Jojoa Acosta, Asesor Andrey Fernando Salas Jaime Andrés Rodríguez Jimmy Velásquez

A quienes participaron en la fase de investigación y experimento: Álvaro José Cervelión C. Jhon Alejandro Botina Jhon Alexander Yela

Al Departamento de Ingeniería Electrónica. Por apoyar nuestra idea y permitirnos la realización de este proyecto

# **TABLA DE CONTENIDO**

|    |                 |        |                                                        | Pág. |

|----|-----------------|--------|--------------------------------------------------------|------|

|    | IN <sup>-</sup> | TRODI  | JCCIÓN                                                 | 19   |

|    | JU              | STIFIC | CACIÓN                                                 | 20   |

| 1. | OE              | BJETIV | OS                                                     | 21   |

|    | 1.1             | OBJI   | ETIVO GENERAL                                          | 21   |

|    | 1.2             | OBJI   | ETIVOS ESPECIFICOS                                     | 21   |

| 2. | MA              | ARCO   | TEÓRICO                                                | 23   |

|    | 2.1             | ANT    | ECEDENTES                                              | 23   |

|    | 2.2             | SIST   | EMAS EMBEDIDOS                                         | 24   |

|    | 2.2             | 2.1    | ¿Qué es un sistema embebido?                           | 25   |

|    | 2.2             | 2.2    | Algunos ejemplos                                       | 26   |

|    | 2.2             | 2.3    | Características de los sistemas embedidos              | 27   |

|    |                 | 2.2.3. | 1 Arquitectura de los sistemas embebidos               | 28   |

|    |                 |        | 2 Software en los sistemas embebidos                   |      |

|    | 2.2             |        | Historia y situación actual de los sistemas embebidos  |      |

|    | 2.3             |        | CA DE DESARROLLO MINI2440                              |      |

|    | 2.3             |        | Arquitectura interna de la MINI2440                    |      |

|    |                 |        | 1 Microprocesador ARM S3C2440AL                        |      |

|    |                 |        | 2 Otros subsistemas importantes en la MINI2440         |      |

|    | 2.3             |        | Software en la MINI2440                                |      |

|    |                 |        | 1 Sistemas operativos                                  |      |

|    |                 |        | 2 Bootloaders o gestores de arranque                   |      |

|    | 2.4             |        | SCILOSCOPIO                                            |      |

|    | 2.4             |        | ¿Qué es un Osciloscopio?                               |      |

|    | 2.4             |        | ¿Qué muestra un Osciloscopio?                          |      |

|    | 2.4             |        | Funcionamiento del Osciloscopio                        |      |

|    |                 |        | 1 Osciloscopio Análogo                                 |      |

|    |                 |        | 2 Osciloscopio Digital                                 |      |

|    | 2.4             |        | Tipos de Osciloscopio Digital                          |      |

|    |                 |        | 1 Osciloscopio de memoria digital                      |      |

|    |                 |        | 2 Osciloscopio de fósforo digital                      |      |

|    | <u> </u>        |        | 3 Osciloscopio de muestreo                             |      |

|    | 2.4             | ⊦.5    | Factores que influyen en la calidad de un Osciloscopio | 66   |

| 2.4.5.1 Ancho de banda                                                         | 66               |

|--------------------------------------------------------------------------------|------------------|

| 2.4.5.2 Precisión de la ganancia                                               | 67               |

| 2.4.5.3 Relación señal a ruido (SNR)                                           | 67               |

| 2.4.5.4 Errores de cuantizacion                                                | 67               |

| 3. DISEÑO Y DESARROLLO DEL DISPOSITIVO                                         | 72               |

| 3.1 HARDWARE                                                                   | 73               |

| 3.1.1 Selección de la arquitectura                                             | 73               |

| 3.1.2 Funcionamiento y diagrama de bloques                                     | 73               |

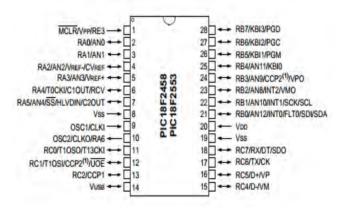

| 3.1.3 El Microcontrolador PIC18F2553                                           | 74               |

| 3.1.3.1 Módulo ADC del Microcontrolador                                        | 77               |

| 3.1.3.2 Módulo de comunicación serial EUSART                                   | 86               |

| 3.1.4 Etapa de entrada y acondicionamiento de la señal                         | 94               |

| 3.1.4.1 Sección vertical                                                       | 95               |

| 3.1.4.2 Bloque comparador de tensión                                           | 103              |

| 3.1.4.3 Bloque sumador DC                                                      | 108              |

| 3.1.5 Esquema final de la placa de adquisición de datos implementada           |                  |

| 3.1.6 Fuente de alimentación                                                   | 112              |

| 3.2 FIRMWARE                                                                   | 112              |

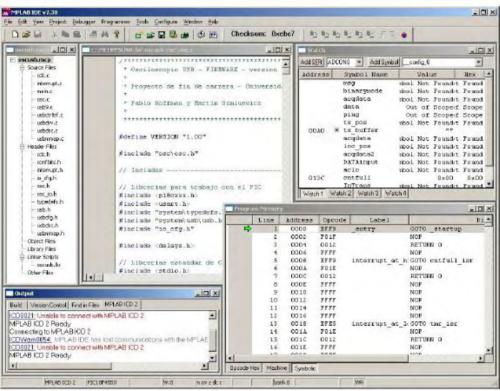

| 3.2.1 Herramienta de trabajo                                                   | 113              |

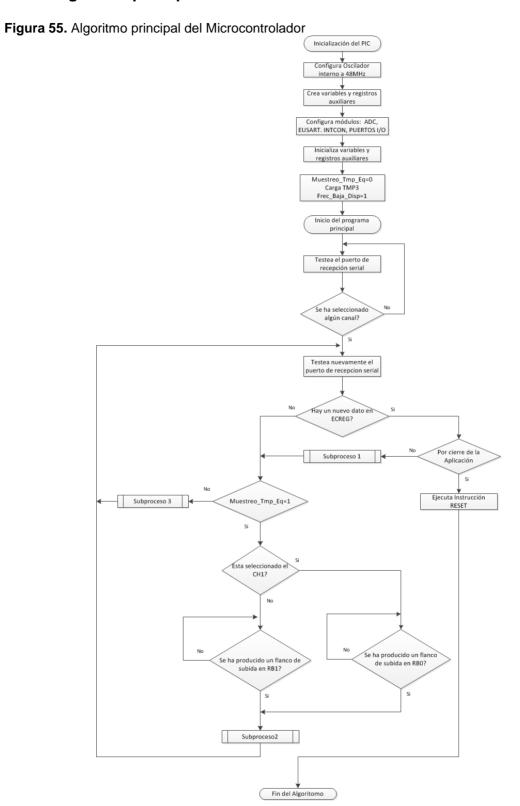

| 3.2.2 Algoritmo principal del Microcontrolador                                 | 114              |

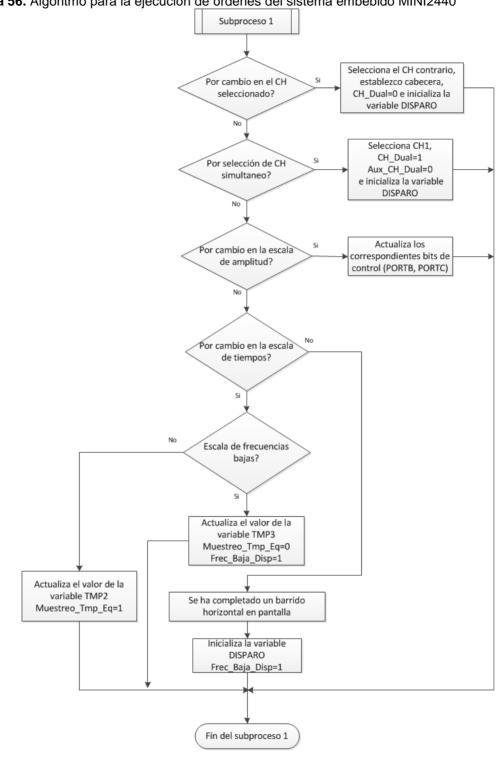

| 3.2.3 Algoritmo para la ejecución de ordenes del sistema embebido MINI244      | <sub>0</sub> 115 |

| 3.2.4 Algoritmo para el control del disparo y conversión de la señal de entrac | Ja118            |

| 3.2.5 Algoritmo para el muestreo de señales de baja frecuencia                 |                  |

| 3.3 SOFTWARE                                                                   | 121              |

| 3.3.1 Selección de herramientas                                                |                  |

| 3.3.1.1 Lenguaje de programación                                               |                  |

| 3.3.1.2 La plataforma de desarrollo .NET Framework                             |                  |

| 3.3.1.3 Entorno de desarrollo                                                  | 124              |

| 3.3.1.4 Visual Studio 2005 y .NET Compact Framework                            |                  |

| 3.3.2 Estructura del software                                                  |                  |

| 3.3.2.1 Biblioteca de clases de. NET Compact Framework utilizadas              |                  |

| 3.3.2.2 Clases y métodos utilizados en el desarrollo de la aplicación          |                  |

| 3.3.3 Funcionamiento del software                                              |                  |

| 3.3.3.1 Control de la interfaz gráfica                                         |                  |

| 3.4 CONSTRUCCION DEL DISPOSITIVO                                               |                  |

| 3.4.1 Materiales y componentes utilizados                                      |                  |

| 3.4.2 Diseño de las placas PCB                                                 |                  |

| 3.4.3 Diseño y construcción de la carcasa                                      | 139              |

|    | 3.4.4  | Presupuesto total del equipo       | 141 |

|----|--------|------------------------------------|-----|

| 4. | RESUL  | .TADOS                             | 143 |

|    | 4.1 CA | ARACTERIZACIÓN DEL EQUIPO          | 143 |

|    | 4.1.1  | Características eléctricas         | 143 |

|    | 4.1.2  | Linealidad                         | 143 |

|    | 4.1.3  | Ruido                              | 144 |

|    | 4.2 PR | RUEBA DE FUNCIONAMIENTO DEL EQUIPO | 145 |

| 5. | CONCL  | LUSIONES                           | 149 |

|    | BIBLIO | GRAFIA                             | 150 |

# **LISTA DE FIGURAS**

|           |                                                                                                      | Pág.     |

|-----------|------------------------------------------------------------------------------------------------------|----------|

| Figura 1  |                                                                                                      |          |

| Figura 2  |                                                                                                      |          |

| Figura 3  |                                                                                                      |          |

| Figura 4  |                                                                                                      |          |

| Figura 5  |                                                                                                      |          |

| Figura 6  |                                                                                                      |          |

| Figure 7  |                                                                                                      |          |

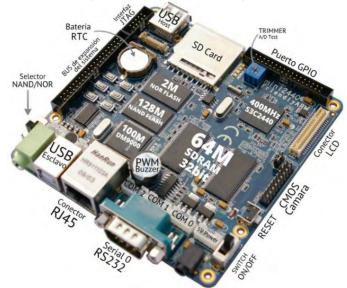

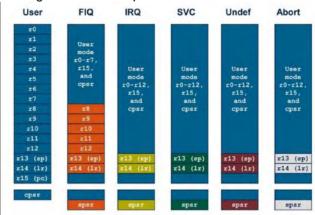

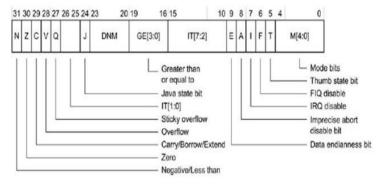

| Figure 8  | Esquema de los registros del microprocesador S3C2440AL  Esquema del registro CPSR/SPSR del S3C2440AL |          |

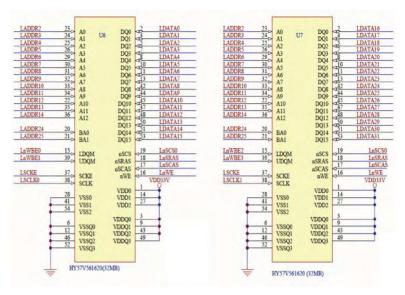

| Figure 1  | Esquema de las 2 memorias Flash incorporadas en la MINI2440                                          | 40<br>40 |

|           | Sistema de almacenamiento SDRAM en la MINI2440                                                       |          |

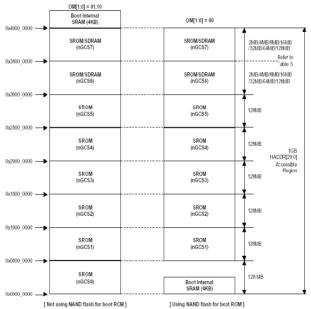

|           | 2. Disposición de la memoria dependiendo del modo de arranque                                        |          |

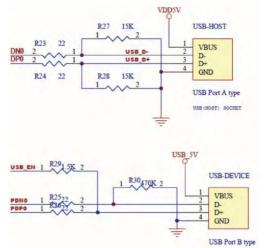

|           | 3. Esquema interno de las interfaces USB con las cuales cuenta la MINI2440                           |          |

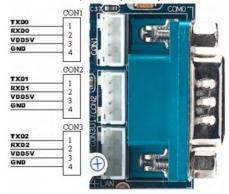

|           | 4. Aspecto fisico de los 3 puertos seriales (UART0, UART1, UART2), incorporados                      |          |

| 3         | MINI2440                                                                                             |          |

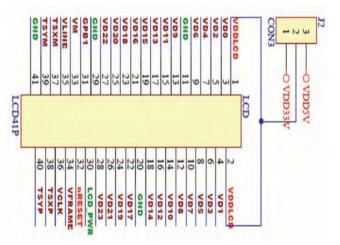

| Figura 1  | 5. Esquema de chip LCD41P, para la interfaz con el display LCD                                       | 53       |

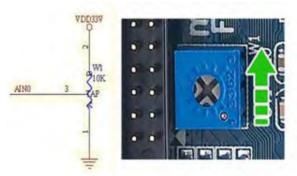

|           | 6. Conexión física del pin AINO al potenciómetro de 10K para testear el ADC con e                    |          |

|           | cuenta la MINI2440                                                                                   |          |

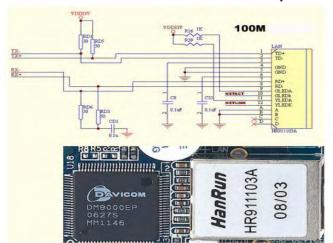

|           | 7. Chip DM9000 10/100M LAN con transformadores de red y un conector RJ-45                            |          |

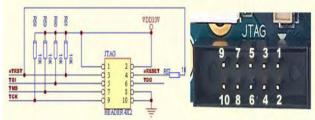

|           | 8. Interfaz JTAG incorporada en la MINI2440                                                          |          |

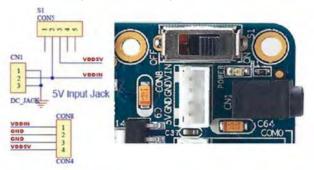

|           | 9. Aspecto físico del CON8, presente en la placa MINI2440                                            |          |

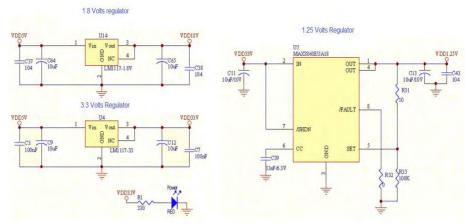

| Figura 2  | D. Reguladores de voltaje incorporado en la MINI2440, encargado de suministrar t                     |          |

|           | de 3.3v, 1.8v y 1.25v                                                                                |          |

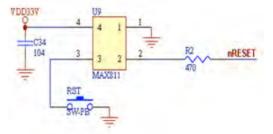

|           | 1. Conexión del botón RESET al chip MAX811                                                           |          |

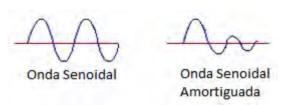

|           | 2. Onda senoidal                                                                                     |          |

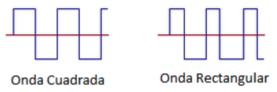

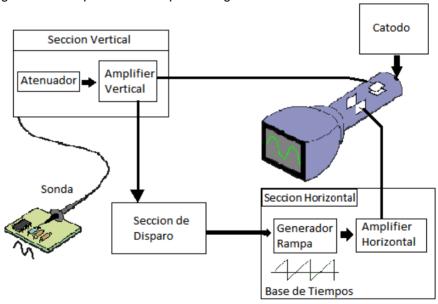

|           | 3. Onda triangular                                                                                   |          |

|           | 4. Onda cuadrada o rectangualar                                                                      |          |

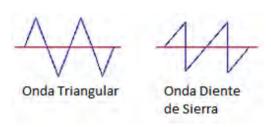

|           | 5. Diagrama de bloques Osciloscopio análogo                                                          |          |

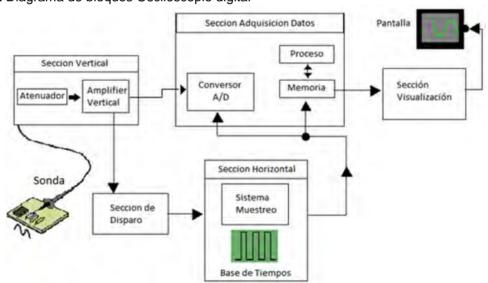

|           | 7. Bloques osciloscopio de memoria digital                                                           |          |

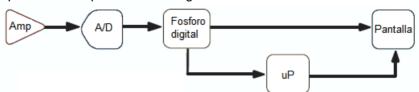

|           | 8. Bloques osciloscopio de memoria digital                                                           |          |

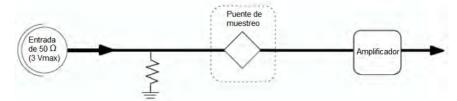

| Figura 2  | 9. Bloques osciloscopio de muestreo                                                                  | 66       |

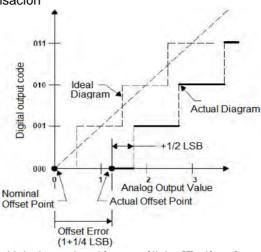

|           | D. Error de compensación                                                                             |          |

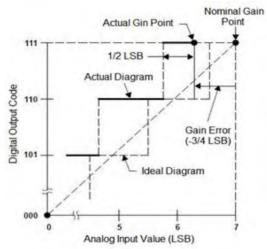

|           | 1. Error de ganancia                                                                                 |          |

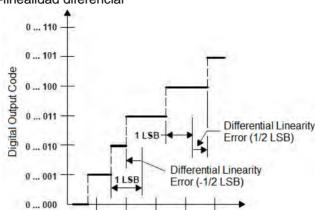

|           | 2. Error de no-linealidad diferencial                                                                |          |

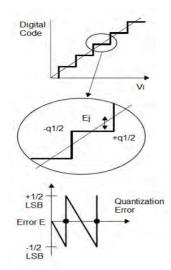

|           | 3. Error de cuantizacion                                                                             |          |

|           | 4. Diagrama de bloques del Osciloscopio Digital implementado                                         |          |

| Figura 3  | 5. Pin-out del microcontrolador PIC18F2553                                                           | 76       |

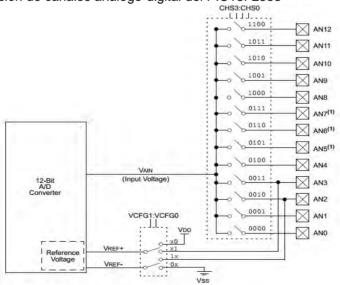

| Figura 3  | 6. Multiplexación de canales análogo-digital del PIC18F2553                                          | 80       |

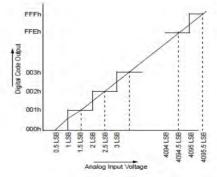

| Figura 3  | 7. Función de transferencia del conversor análogo-digital del PIC18F2553                             | 81       |

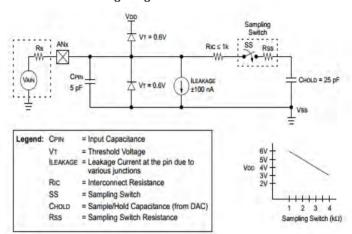

|           | B. Modelo del conversor análogo-digital del PIC18F2553                                               |          |

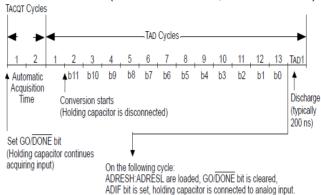

| Figura 3  | 9. Operación del conversor A/D (ACQT <2:0>=001, TACQ = 2TAD)                                         | 86       |

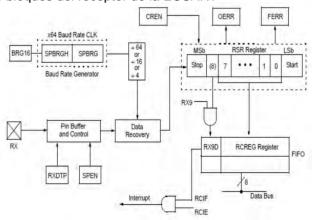

| Figura 4  | Diagrama de bloques del transmisor de la EUSART.                                                     | 89       |

|           | 1. Diagrama de bloques del receptor de la EUSART                                                     |          |

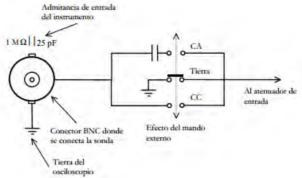

|           | 2. Selector de acoplamiento de entrada (AC-GND-DC)                                                   |          |

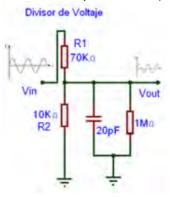

|           | 3. Esquema del atenuador de entrada implementado (Divisor de Voltaje)                                |          |

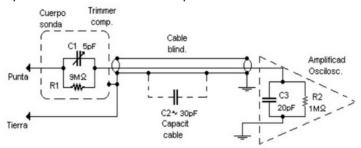

| ⊢iniira ⊿ | Circuito equivalente de una sonda compensada                                                         | 99       |

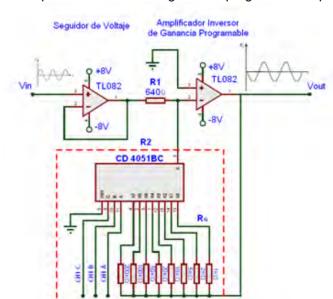

|           | . Esquema del amplificador inversor de ganancia programable implementado                |      |

|-----------|-----------------------------------------------------------------------------------------|------|

| Figura 46 | . Esquema del A.O. configuradocomo comparador de tensión                                | 104  |

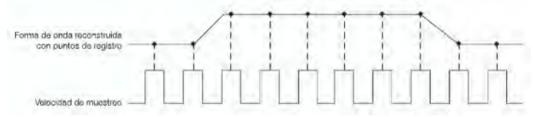

| Figura 47 | . Método de muestreo en tiempo real                                                     | 105  |

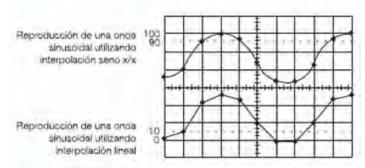

| Figura 48 | . Interpolación lineal y seno x/x                                                       | 106  |

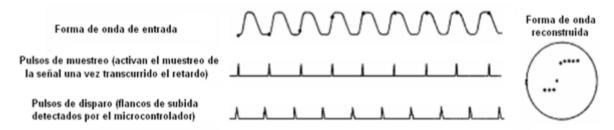

| Figura 49 | . Presentación de una señal muestreada en tiempo equivalente aleatorio y secuencial     |      |

|           | respectivamente                                                                         | 107  |

| Figura 50 | . Formas de onda correspondiente al muestreo en tiempo equivalente secuencial           | 108  |

| Figura 51 | . Esquema del bloque sumador DC, incorporado previo a la entrada del ADC interno el     | n el |

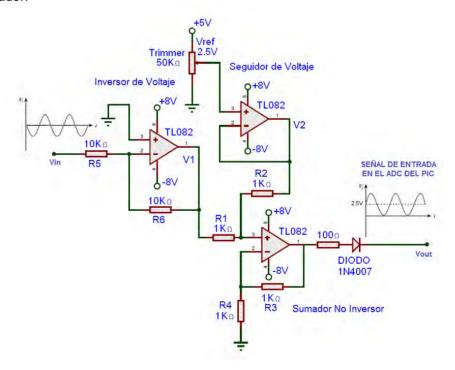

|           | microcontrolador                                                                        | 109  |

| Figura 52 | . Esquema final de la placa de adquisición de datos incorporada en el dispositivo       | 111  |

| Figura 53 | . Diagrama de conexiones de la fuente de alimentación eléctrica                         | 112  |

|           | . Captura de Pantalla de MPLAB V.8.70                                                   |      |

| Figura 55 | . Algoritmo principal del Microcontrolador                                              | 114  |

| Figura 56 | . Algoritmo para la ejecución de órdenes del sistema embebido MINI2440                  | 116  |

| Figura 57 | . Algoritmo para el control de disparo de la conversión de la señal de entrada          | 118  |

| Figura 58 | . Algoritmo para el muestreo de señales de baja frecuencia                              | 120  |

|           | . Arquitectura de la infraestructura de desarrollo                                      |      |

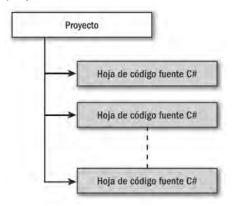

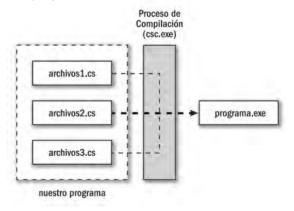

| Figura 60 | . Organización de un proyecto en Visual Studio 2005                                     | 125  |

|           | . Organización de una solución en Visual Studio 2005                                    |      |

| Figura 62 | . Compilación de un proyecto                                                            | 126  |

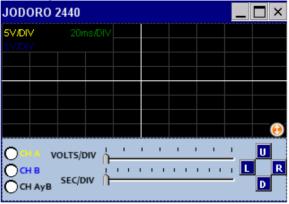

| Figura 63 | . GUI desplegada en la pantalla del sistema embebido MINI2440                           | 131  |

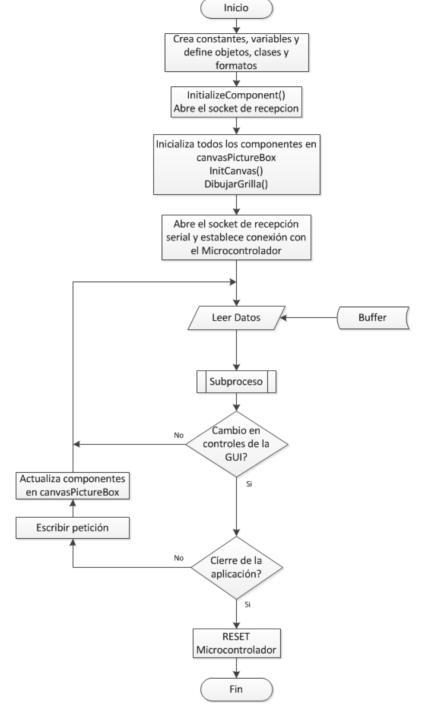

| Figura 64 | . Algoritmo principal de la aplicación ejecutada por el sistema embebido MINI2440       | 132  |

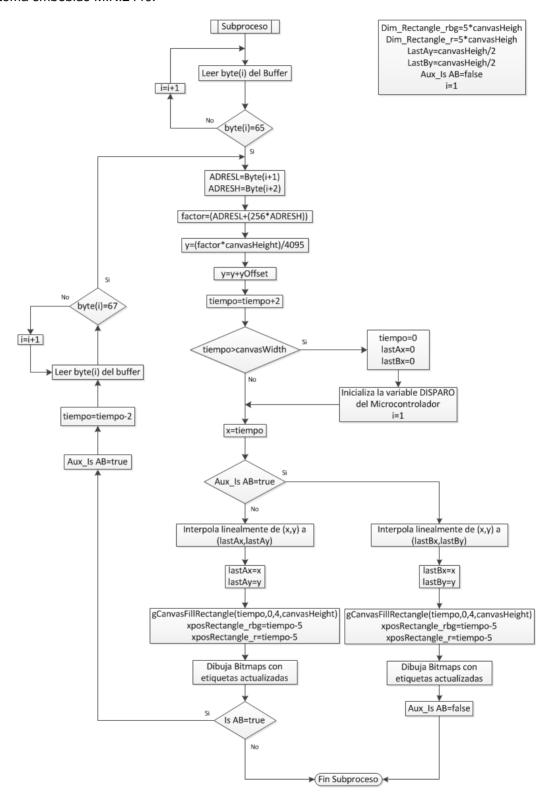

| Figura 65 | . Algoritmo del subproceso ejecutado por la aplicación gráfica implementada en el siste |      |

|           | embebido MINI2440                                                                       |      |

|           | . Método de planchado                                                                   |      |

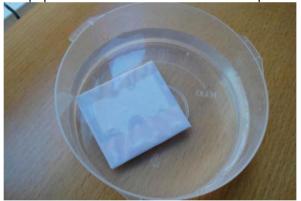

|           | . Placa adherida al papel satinado e introducida en un recipiente con agua              |      |

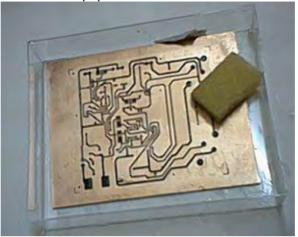

|           | . Placa después de retirar el papel                                                     |      |

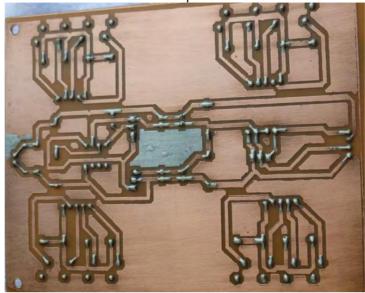

|           | . Placa de la tarjeta de adquisición de datos después de retirar el cobre               |      |

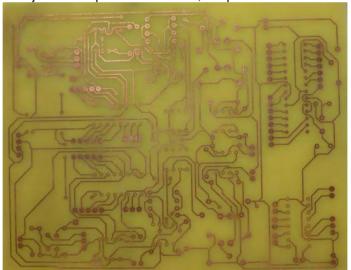

|           | . Placa fuente de alimentación después de retirar el cobre                              |      |

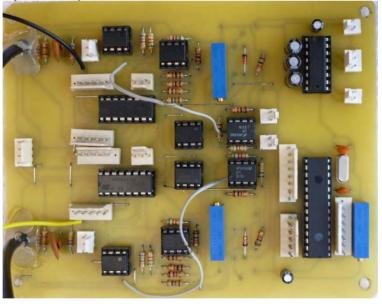

|           | . Placa de la tarjeta de adquisición de datos soldada                                   |      |

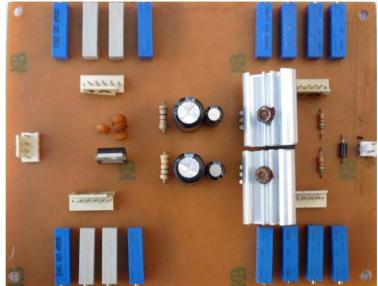

|           | . Placa de la fuente de alimentación soldada                                            |      |

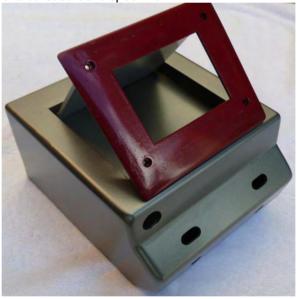

|           | . Vista interna de la carcasa del dispositivo                                           |      |

|           | . Vista frontal de la carcasa del dispositivo                                           |      |

|           | . Vista posterior de la carcasa del dispositivo                                         |      |

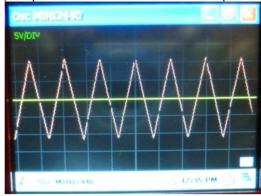

|           | . Señal triangular (comprobación de linealidad en el dispositivo)                       |      |

|           | . Señal de ruido interno del dispositivo                                                |      |

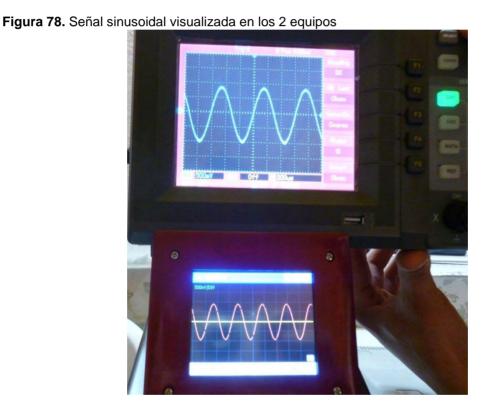

|           | . Señal sinusoidal visualizada en los 2 equipos                                         |      |

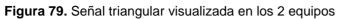

|           | . Señal triangular visualizada en los 2 equipos                                         |      |

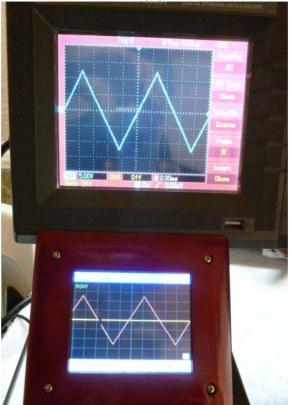

|           | . Señal cuadrada o rectangular visualizada en los 2 equipos                             |      |

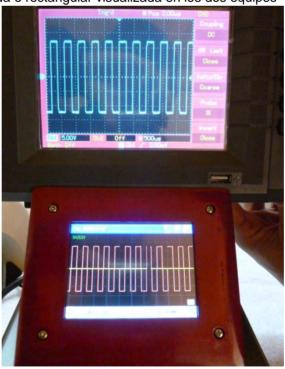

|           | . Señal sinusoidal, de baja frecuencia (101Hz) y con Amplitud de 12Vpp                  |      |

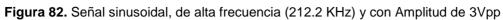

| Figura 82 | . Señal sinusoidal, de alta frecuencia (212.2 KHz) y con Amplitud de 3Vpp               | 148  |

# LISTA DE TABLAS

| Toble 1              |                                                                                    | Pág.       |

|----------------------|------------------------------------------------------------------------------------|------------|

| Tabla 1.<br>Tabla 2. | Sistemas operativos embebidos vigentes hasta el año 2009                           |            |

| Tabla 3.             | Tipos y Modos de excepción                                                         |            |

| Tabla 4.             | Características Microcontrolador PIC18F2553                                        |            |

| Tabla 5.             | Registro ADCON0 (FC2h): Registro 0 DE Control A/D                                  |            |

| Tabla 6.             | CHS3:CHS0: Bits de selección del canal análogo.                                    |            |

|                      | GO/DONE: Bit de inicio y monitorización del estado de la Conversión A/D            | <i>1</i> 1 |

|                      | ADON: Bit de Inicio y Monttonzación del estado de la Conversión A/D                |            |

|                      | Registro ADCON1 (FC1h): Registro 1 de Control A/D.                                 |            |

| Tabla 10             | VCFG1: Bit de configuración de la tensión de referencia VREF                       | 70         |

|                      | VCFG0: Bit de configuración de la tensión de referencia VREF+                      |            |

|                      | PCFG3:PCFG0: Bits de configuración de los puertos de conversión A/D.               |            |

|                      | Registro ADCON2 (FC0h): Registro 2 de control A/D.                                 |            |

|                      | ADFM: Bit de justificación del resultado de la conversión                          |            |

|                      | ACQT2:ACQT0: Bits de configuración del tiempo de adquisición para la Conversión.   |            |

|                      | ADCS2:ADCS0: Bits de configuración de la señal de reloj para el Conversor A/D      |            |

|                      | TAD vs Frecuencia de operación del dispositivo.                                    |            |

|                      | Registro TXSTA (FACh): Registro de estado y control de transmisión                 |            |

|                      | CSRC: Bit de selección de la fuente de señal de reloj para el modo síncrono        |            |

|                      | TX9: Bit de habilitación del modo de 9 bits en transmisión.                        |            |

|                      | TXEN: Bit de habilitación de la transmisión.                                       |            |

|                      | SYNC: Bit de selección del modo de trabajo de la EUSART.                           |            |

|                      | SENDB: Bit de envió del carácter de BREAK en modo asíncrono                        |            |

|                      | BRGH: Bit de selección del modo de alta velocidad en modo asíncrono.               |            |

|                      | TRMT: Bit de estado del registro de desplazamiento de transmisión.                 |            |

|                      | Registro RCSTA (FABh): Registro de estado y control de recepción                   |            |

|                      | SPEN: Bit de activación del puerto serie.                                          |            |

|                      | RX9: Bit de habilitación del modo de 9 bits en transmisión                         |            |

|                      | SREN: Bit de habilitación de la recepción simple en modo síncrono Maestro          |            |

|                      | CREN: Bit de habilitación de la recepción.                                         |            |

|                      | ADDEN: Bit de habilitación de la dirección para el modo asíncrono de 9 bits        |            |

|                      | FERR: Bit de error de formato (solo lectura).                                      |            |

|                      | OERR: Bit de error de sobrescritura (solo lectura).                                |            |

|                      | Registro BAUDCON (FB8h): Registro de estado y control de los baudios               |            |

|                      | ABDOVF: Bit de desbordamiento de auto-detección de la velocidad de comunicación.   |            |

|                      | RCIDL: Bit de estado de la operación de recepción                                  |            |

| Tabla 37.            | SCKP: Bit de selección de polaridad de la señal de reloj en modo síncrono          | 92         |

|                      | BRG16: Bit de habilitación del generador de velocidad de 16 bits (SPBRG y SPBRGH   |            |

|                      | WUE: Bit de habilitación del modo de auto-activación en modo asíncrono.            |            |

|                      | ABDEN: Bit de habilitación del modo de auto-detección de velocidad de comunicación |            |

| Tabla 41.            | Calculo de velocidades de transmisión.                                             | 93         |

| Tabla 42.            | Párametros de trabajo del multiplexor CD4051BC                                     | .100       |

|                      | Párametros para el cálculo de las ganancias en el PGA                              |            |

|                      | Ganacias calculadas para cada factor de escala                                     |            |

|                      | Resistencia de realimntación calculada para cada factor de escala seleccionado     |            |

|                      | Presupuesto total del dispositivo                                                  |            |

|                      | Caracteristicas electricas del Osciloscopio                                        |            |

## **LISTA DE ANEXOS**

ANEXO A: Manual de usuario para manejo del prototipo del Osciloscopio Digital.

**ANEXO B:** CD-ROM con los siguientes archivos:

- Manual de usuario para la construcción del Entorno de Desarrollo Integrado (IDE), necesario para trabajar con el sistema embebido MINI2440.

- Software de la interfaz gráfica de usuario (GUI) desarrollada bajo Microsoft Visual Studio 2005.

- Carpeta con los programas (código fuente) de control del PIC y visualización en la MINI2440 (software) desarrollados.

- Planos de la estructura externa y circuitos impresos diseñados.

- Fotografías y videos de la construcción del prototipo.

#### **GLOSARIO**

ALIASING: Corresponde al efecto que causa que señales continuas distintas se tornen indistinguibles cuando se muestrean digitalmente.

ARM: (Advanced RISC Machines). Arquitectura RISC de 32 bits desarrollada por ARM Holdings, la relativa simplicidad de los procesadores ARM los hace ideales para aplicaciones de baja potencia.

BAUDIO: Unidad de medida, utilizada en telecomunicaciones, que representa la cantidad de veces que cambia el estado de una señal en un periodo de tiempo, tanto para señales digitales como para señales analógicas.

CARCASA: Conjunto de piezas duras y resistentes, que dan soporte (internas) o protegen (externas) a otras partes de un equipo.

CODIFICACIÓN: Proceso que consiste en la traducción de los valores de tensión eléctrica analógicos que ya han sido previamente cuantificados (ponderados) al sistema binario, mediante códigos preestablecidos.

CUANTIFICACIÓN: Etapa del proceso de digitalización de señales, que consiste en convertir una sucesión de muestras de amplitud continúa en una sucesión de valores discretos preestablecidos según el código utilizado.

DIGITALIZACIÓN: Consiste básicamente en realizar de forma periódica medidas de la amplitud (tensión) de una señal, redondear sus valores a un conjunto finito de niveles preestablecidos de tensión y registrarlos como números enteros en cualquier tipo de memoria o soporte.

DRAM: Memoria dinámica de acceso aleatorio que se usa principalmente en los módulos de memoria RAM como memoria principal del sistema.

FIRMWARE: Bloque de instrucciones de máquina para propios específicos, grabado en una memoria de tipo de solo lectura (ROM, EEPROM, flash, etc), que establece la lógica de más bajo nivel que controla los circuitos electrónicos de un dispositivo de cualquier tipo.

GPIO: (General Purpose Input/Output), puertos de expansión de Entrada y Salida, presentes en cualquier tipo de Hardware.

GUI: Programa informático que actúa de interfaz de usuario, utilizando un conjunto de imágenes y objetos gráficos para representar la información y acciones disponibles en la interfaz.

MUESTREO: Etapa del proceso de digitalización de señales, que consiste en tomar muestras de una señal analógica a una frecuencia o tasa de muestreo constante, para cuantificarlas posteriormente.

PAGER: (También llamado dispositivo de radio búsqueda o radio mensajería), es un dispositivo de telecomunicaciones muy simple utilizado para la recepción de mensajes de texto cortos.

RISC: (Reduced Instruction Set Computer). Conjunto de Instrucciones Reducido. Corresponde a un tipo de arquitectura de computadora que promueve conjuntos pequeños y simples de instrucciones, los cuales toman poco tiempo para ejecutarse.

SDRAM: Memoria de acceso aleatorio DRAM que tiene una interfaz síncrona.

#### **RESUMEN**

El presente proyecto consiste en el desarrollo del prototipo de un dispositivo digital de captura de señales eléctricas (conocido con el nombre de osciloscopio), implementado sobre el sistema embebido MINI2440.

El osciloscopio posee 2 canales de 12 bit de resolución y un ancho de banda de 250KHz, su diseño está basado en una placa que adquiere y transmite de manera serial los datos hacia el sistema embebido MINI2440 a través del protocolo RS-232, para su posterior procesamiento y visualización sobre la pantalla táctil con la cual cuenta el dispositivo.

El diseño de la placa de adquisición de datos está basado en un microcontrolador central de referencia PIC18F2553 y varios componentes (controlados por dicho microcontrolador) con el fin de llevar a cabo la tarea de captura de la señal de entrada.

Además del diseño y construcción del hardware (placa de adquisición de datos), el proyecto contempla el desarrollo del firmware (programa que corre en el PIC para controlar los componentes) y el software (interfaz gráfica que corre sobre el sistema embebido MINI2440 para controlar el osciloscopio).

#### **ABSTRACT**

This project involves the development of the prototype of an electrical signal acquisition device (also known as oscilloscope) implemented on the MINI2440 Embedded System.

The oscilloscope has two 12-bits resolution channels and a bandwidth of 250 KHz, it's design is based on a board that acquires and transmits the data serially to the MINI2440 Embedded System through the RS-232 protocol, for subsequent processing and visualization on the touchscreen that has the device.

The design of the data acquisition board is based on a central microcontroller PIC18F2553 core and multiple components (controlled by such processor) which take of the whole acquisition task.

Besides design and building of the hardware (acquisition data board), this project includes the development of firmware (program which runs on the microcontroller) and software (graphical interface that runs on the MINI2440 Embedded System to control the oscilloscope).

#### **MARCAS REGISTRADAS**

Windows Embedded CE 6.0 y sus respectivas actualizaciones R2 y R3, al igual que Windows Mobile, Windows Server, Windows Vista, SQL Server, Visual Basic, Visual C#, Visual Studio, Windows XP y Win7, son marcas registradas de Microsoft Corporation<sup>®</sup> en Estados Unidos y en otros países.

MPLAB IDE, es una marca registrada de MICROCHIP<sup>®</sup>.

**PROTEUS**, es una marca registrada de Proteus-Hubor<sup>®</sup>.

**AutoCAD**, es una marca registrada de Autodesk<sup>®</sup>.

MINI2440, es una marca registrada de FriendlyARM<sup>®</sup>.

PIC18F2553, es una marca registrada por MICROCHIP<sup>®</sup>.

**CD4051BC Single 8-Channel Analog Mux**, es una marca registrada de National Semiconductor<sup>®</sup>.

A.O. LM311, A.O. TL082, son una marca registrada de STMicroelectronics®

# INTRODUCCIÓN

Los niveles de integración actuales permiten construir sistemas cada vez más pequeños, veloces y de menor consumo de potencia, lo cual ha favorecido su difusión en casi todas las actividades humanas, a medida que se extiende el campo de aplicación de estos sistemas digitales, lo hacen las exigencias de funcionamiento a ellos impuestas; nuevos retos de diseño se presentan a medida que los sistemas embebidos se integran a las actividades humanas.

Un sistema embebido consiste en un sistema de computación cuyo hardware y software están específicamente diseñados y optimizados para resolver un problema concreto eficientemente, además pueden hacer parte de un dispositivo o máquina mayor, que cumple funciones de monitoreo o control. Algunos sistemas embebidos incluyen un sistema operativo, pero muchos son tan especializados que toda la lógica puede implementarse en un solo programa.

La característica principal que diferencia a los "embebidos" de los demás sistemas electrónicos es que al estar insertados dentro del dispositivo que controlan, están sujetos en mayor medida a cumplir requisitos de tamaño, fiabilidad, consumo energético y costo, y su existencia puede no ser aparente. Algunos ejemplos de Sistemas embebidos son los sistemas de información integrados en automóviles, trenes o aviones, y controladores de procesos en sistemas de producción industrial.

La gran aplicabilidad de los Sistemas embebidos en cualquier ámbito sectorial, así como el valor añadido que aportan los mismos a los equipos que los contienen, hacen que el desarrollo de aplicaciones que den solución a problemas de ingeniería llevadas a cabo sobre estos sistemas se convierta en una alternativa innovadora a nivel institucional, que fácilmente podría abrir una nueva línea de investigación enfocada al desarrollo de aplicaciones en este tipo de sistemas.

# **JUSTIFICACIÓN**

Fundaciones para el desarrollo tecnológico<sup>1</sup>, al igual que Instituciones Universitarias a través de grupos de investigación a nivel de Iberoamérica<sup>2</sup>, Ilevan actualmente a cabo importantes proyectos enfocados en el desarrollo de Sistemas embebidos, generando de esta manera una apertura en cuanto a la transferencia tecnológica y de conocimiento, no solo en el desarrollo de estos sistemas, sino también en las aplicaciones que es posible implementar sobre estos, permitiendo así el diseño y construcción de equipos que cuenten con un valor agregado en cuanto al tamaño, costo, consumo de potencia y velocidad de procesamiento.

Sumado a lo anterior, la disminución dramática en el costo de los dispositivos semiconductores (generalmente llamadas placas de desarrollo) necesarios para implementar cualquier tipo de aplicación, son factores de peso que constituyen una razón fundamental por la cual se decide llevar a cabo el desarrollo de una aplicación sobre el sistema embebido MINI2440 en particular.

El proceso de investigación en el sistema embebido MINI2440, está enfocado principalmente a ofrecer un conjunto de conocimientos en cuanto al manejo de la placa de desarrollo, con el fin de poder implementar cualquier tipo de aplicación orientada a resolver un problema específico de ingeniería, y de esta manera contar con un equipo liviano, de menor tamaño, bajo consumo de potencia y una alta velocidad de procesamiento en cuanto a la ejecución de tareas.

Se pretende que los estudiantes del programa de Ingeniería Electrónica de la Universidad de Nariño cuenten con una alternativa innovadora en el desarrollo de sus proyectos, basadas particularmente en el sistema embebido MINI2440, aprovechando así el gran aporte que actualmente ofrece el acelerado desarrollo de los sistemas embebido.

<sup>&</sup>lt;sup>1</sup> Fundación OPTI. Fundación ASCAMM. Tendencias y aplicaciones de los sistemas embebidos Septiembre 2009 [En línea].

<sup>&</sup>lt;a href="http://www.opti.org/publicaciones/pdf/texto131.pdf">http://www.opti.org/publicaciones/pdf/texto131.pdf</a>

<sup>&</sup>lt;sup>2</sup> Camargo B, Carlos Iván. Transferencia tecnológica y de comunicaciones en el diseño de sistemas embebidos.

Agosto 13 2011 [En línea].

<sup>&</sup>lt;a href="http://www.bdigital.unal.edu.com/5696/1/carlosivancamargobare%C3%B10">http://www.bdigital.unal.edu.com/5696/1/carlosivancamargobare%C3%B10</a> 2011.pdf>

#### 1. OBJETIVOS

#### 1.1 OBJETIVO GENERAL

Desarrollar un dispositivo de medición electrónico que permita la visualización y el control en los parámetros de medida de señales eléctricas en tiempo real, a través de una aplicación gráfica implementada sobre el sistema embebido MINI2440.

## 1.2 OBJETIVOS ESPECIFICOS

- Adquirir conocimientos básicos en cuanto al funcionamiento y la arquitectura interna de los sistemas embebidos en general, así como también al papel que actualmente juegan estos sistemas de computación en el desarrollo de dispositivos electrónicos de propósito específico.

- Apropiarse del conocimiento suficiente acerca del funcionamiento, la arquitectura interna y los recursos de hardware y software con los cuales cuenta el sistema embebido MINI2440.

- Llevar a cabo la construcción de un entorno apropiado para el desarrollo (edición, compilación y depuración del código fuente) de aplicaciones basadas en la plataforma .NET de Microsoft, las cuales posteriormente serán ejecutadas sobre el sistema embebido MINI2440.

- Implementar un Sistema Operativo dedicado, basado en Microsoft Windows, sobre el sistema embebido MINI2440, que permita ejecutar aplicaciones basadas en el .NET Compact Framework de la plataforma .NET de Microsoft.

- Utilizar un lenguaje de alto nivel (HLL), en el desarrollo de una aplicación gráfica para el sistema embebido MINI2440, la cual despliegue en la pantalla del dispositivo una amigable GUI (Interfaz Gráfica de Usuario), para el control de los diferentes parámetros de medida del dispositivo y la visualización de las señales eléctricas de entrada.

- Diseñar e implementar una etapa previa al sistema embebido MINI2440, que permita la adquisición, adaptación y conversión digital de las señales análogas de entrada.

| • | Verificar el correcto funcionamiento del prototipo final, utilizando un dispositivo electrónico de laboratorio, denominado generador de formas de onda. |  |  |  |  |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|   |                                                                                                                                                         |  |  |  |  |

|   |                                                                                                                                                         |  |  |  |  |

|   |                                                                                                                                                         |  |  |  |  |

|   |                                                                                                                                                         |  |  |  |  |

|   |                                                                                                                                                         |  |  |  |  |

|   |                                                                                                                                                         |  |  |  |  |

|   |                                                                                                                                                         |  |  |  |  |

|   |                                                                                                                                                         |  |  |  |  |

|   |                                                                                                                                                         |  |  |  |  |

|   |                                                                                                                                                         |  |  |  |  |

|   |                                                                                                                                                         |  |  |  |  |

|   |                                                                                                                                                         |  |  |  |  |

|   |                                                                                                                                                         |  |  |  |  |

|   |                                                                                                                                                         |  |  |  |  |

|   |                                                                                                                                                         |  |  |  |  |

|   |                                                                                                                                                         |  |  |  |  |

|   |                                                                                                                                                         |  |  |  |  |

|   |                                                                                                                                                         |  |  |  |  |

# 2. MARCO TEÓRICO

#### 2.1 ANTECEDENTES

En el documento final del trabajo de grado "Implementación de un sistema teleoperado con realimentación visual para evasión de obstáculos de un robot móvil", presentado en el año 2012 por Luis Miguel Betancourt y Nelson Alfonso Boton Gómez, en la Universidad Militar Nueva Granada. Se implementa un sistema teleoperado con realimentación visual, utilizando el sistema embebido MINI2440 montado sobre el robot móvil con el propósito de controlarlo desde un computador distante, que se comunica con el sistema (MINI2440-Robot Móvil) por medio del protocolo TCP. El usuario recibe la imagen enviada por el sistema y será capaz de controlar el movimiento del robot al enviar señales de control por medio del protocolo TCP.

En el año 2011, en la Universidad Tecnológica de Malasya, fue llevado a cabo el proyecto de investigación y desarrollo, "Development of a Portable Heart Beat Monitor Unit Using Friendly ARM MINI2440"<sup>4</sup>, desarrollado por Mat Taib Binti Norshazwana, en el cual se diseña y construye una unidad portátil para monitorear el latido del corazón usando la Friendly ARM MINI2440, básicamente consiste en un electrocardiograma personal, implementado sobre el sistema embebido MINI2440, capaz de monitorear el ritmo cardiaco.

En el año 2011, fue presentado el informe final de la tesis "Desarrollo de una interfaz gráfica con pantalla táctil para el manejo de un sistema robótico"<sup>5</sup>, desarrollado por Javier Echeverría Senosiain, en este proyecto se logra sustituir un ordenador de sobremesa que controla un sistema robótico por un equipo de menor tamaño, portátil y manejable.

<sup>&</sup>lt;sup>3</sup> Betancourt, Luis Miguel. Boton G, Nelson Alfonso. Implementación de un sistema teleoperado con realimentación visual para evasión de obstáculos de un robot móvil.

Junio 12 2012 [En línea].

<sup>&</sup>lt; http://repository.unimilitar.edu.co/handle/10654/3299>

<sup>&</sup>lt;sup>4</sup> Norshazwana B, Mat Taib. Development of a Portable Heart Beat Monitor Unit Using Friendly ARM MINI2440.

<sup>2011[</sup>En línea].

<sup>&</sup>lt; http://norlaili.fke.utm.my/human-capital-1>

<sup>&</sup>lt;sup>5</sup> Echeverría Senosiain, Javier. Desarrollo de una interfaz gráfica con pantalla táctil para el manejo de un sistema robótico.

<sup>2011[</sup>En línea].

<sup>&</sup>lt; http://academica-e.unavarra.es/handle/2454/4623 >

En el documento "Instrucción en el diseño de sistemas empotrados. Aplicación al control de un brazo robot" escrito por Houcine Hassan, Javier Soriano, Javier Montagudy Carlos Domínguez. En el año 2003, en la Universidad Politécnica de Valencia (UPV), se presenta una metodología de aprendizaje para el diseño de sistemas empotrados (SE), inspirada en el proyecto Europa de la Universidad Politécnica de Valencia, en el artículo se describe la implementación de dicha metodología en la asignatura de Diseño de Sistemas con Microprocesadores de la Escuela Técnica Superior de Informática Aplicada.

En el documento final del trabajo de grado "Representación de variables eléctricas en el sistema embebido MINI2440", presentado en el año 2011 por Fernando Marcotegui Zabalza, en la Escuela Técnica Superior de Ingenieros Industriales y de Telecomunicaciones de Navarra. Se describe el proceso, que fue llevado a cabo para el monitoreo de una señal análoga en la entrada del módulo ADC del sistema embebido MINI2440.

En el trabajo de grado presentado en el año 2006, denominado "Osciloscopio USB"<sup>8</sup>, desarrollado por Pablo Hoffman y Martin Szmulewicz, en la Universidad ORT de Uruguay, el cual consiste en el desarrollo del prototipo de un osciloscopio digital de captura de señales eléctricas (también conocido con el nombre de osciloscopio) con conexión a la PC a través del puerto USB.

#### 2.2 SISTEMAS EMBEBIDOS

Los sistemas de computación se encuentran en cualquier parte. Es probable que nadie se sorprenda al saber que millones de sistemas de computación son producidos y vendidos cada año, como por ejemplo computadores de escritorio o computadores personales. Sin embargo, sorprende saber que billones de sistemas de computación de propósito específico son construidos y vendidos cada año; los sistemas embebidos se encuentran alrededor de nuestras vidas, en forma de teléfonos móviles, equipos médicos, sistemas de navegación aérea, reproductores MP3, impresoras, automóviles, etc.

<sup>&</sup>lt;sup>6</sup> Houcine Hassan, Javier Doriano. Montagudy Carlos Domínguez. Instrucción en el diseño de un sistema empotrado. Aplicación al control de un brazo robot. 2003[En línea].

<sup>&</sup>lt; http://www.ceautomatica.es/old/actividades/jornadas/XXIV/documentos/econ/90.pdf >

<sup>&</sup>lt;sup>7</sup> Marcotegui Zabalza, Fernando. Representación de variables eléctricas en el sistema embebido Mini2440. 2011[En línea].

<sup>&</sup>lt; http://academica-e.unavarra.es/bitstream/handle/2454/4283/577623.pdf?sequence=1>

<sup>&</sup>lt;sup>8</sup> Hoffman, Pablo. Szmulewicz, Martin. Osciloscopio USB.

Septiembre 13 2006[En línea].

<sup>&</sup>lt; http://pablohoffman.com/cgi-bin/twiki/bin/view/Oscusb/WebHome>

Cada vez que se mira alrededor es posible identificar un dispositivo que contiene un microprocesador, y probablemente se ha encontrado un sistema embebido. Por estas razones resulta conveniente y pertinente estudiarlos.

# 2.2.1 ¿Qué es un sistema embebido?

Dar una descripción precisa de qué es un sistema embebido puede resultar una tarea complicada. El experto en software embebido Michael Barr definía, no sin cierta ambigüedad, un sistema embebido o como: "Una combinación de hardware y software de computadora, sumado tal vez a algunas piezas mecánicas o de otro tipo, diseñada para tener una función específica"

Esta definición se centra en la idea de que los sistemas embebidos en principio son diseñados específicamente para llevar a cabo de manera eficiente una tarea en particular, de tal forma que los recursos utilizados son optimizados para resolver dicho problema en concreto. Un sistema embebido posee hardware de computador junto con software embebido como uno de sus componentes más importantes, por lo tanto debe existir un sistema de computación gobernado por un microprocesador o similares.

Así, un sistema embebido se encontraría en un punto intermedio entre una computadora de propósito general -como por ejemplo una computadora personal (PC), que está diseñada para permitir realizar, idealmente, la mayor variedad posible de tareas- y un sistema que es diseñado por hardware específicamente para una tarea o un conjunto reducido de ellas, como por ejemplo los sistemas tradicionales de control, los dispositivos de lógica programable (PLDs) o las field-programmable gate arrays (FPGAs), que son programados directamente en hardware.

No obstante, en los últimos años han cobrado importancia algunos tipos de dispositivos que, si bien no encajan estrictamente en la definición anterior, comparten ciertas características con el resto de sistemas embebidos y por tanto resulta razonable incluirlos en este grupo. En concreto, los *smartphones* y las computadoras *tablets*, así como las *personal digital assistants* (PDAs), son dispositivos que podríamos situar entre las PCs y los sistemas embebidos, pues aunque no están diseñados para realizar una única función específica, presentan muchas características típicas de estos últimos, como las restricciones en los recursos computacionales disponibles o la manera de desarrollar el software.

25

<sup>&</sup>lt;sup>9</sup> Barr, Michael. Programming Embedded System in C and C++. En: O'Reilly [En línea] N° 1, Enero, 1999.

<sup>&</sup>lt;a href="http://www.embeonline.com/uploads/O'Reilly-programming\_embedded\_systems\_in\_C\_and\_C++.pdf">http://www.embeonline.com/uploads/O'Reilly-programming\_embedded\_systems\_in\_C\_and\_C++.pdf</a>

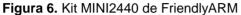

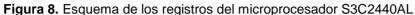

Ante esta cuestión, el citado Michael Barr, desde su perspectiva de desarrollador de software, en la actualidad es partidario de incluir estos últimos dispositivos mencionados en el conjunto de los sistemas embebidos. Siguiendo el mismo razonamiento, en este trabajo se considera que la placa de desarrollo MINI2440 de FriendlyARM, con la cual se llevó a cabo este proyecto, es también un sistema embebido a todos los efectos, ya que su arquitectura es muy similar a una Tablet o una PDA.

# 2.2.2 Algunos ejemplos

Es posible encontrar infinidad de ejemplos de dispositivos que contienen sistemas embebidos y que son empleados en la actualidad a diario en el llamado "primer mundo", en la esfera doméstica, profesional, industrial, científica, militar, etc. Además de los ya mencionados smartphones, tablets y PDAs, a continuación se citan algunos otros:

Relojes digitales: En cualquier dispositivo donde haya un reloj digital existe un sistema embebido, tanto en un reloj de muñeca o en un horno o termómetro digital, por ejemplo. Típicamente, un reloj digital contiene un procesador sencillo de 4 u 8 bits (empleado típicamente para permitir dar soporte con el mismo hardware a una variedad de modelos y características) y su propia ROM integrada.

**Electrodomésticos:** En prácticamente cualquier electrodoméstico fabricado en las últimas décadas se encuentran sistemas embebidos, desde una batidora a una lavadora o a una tostadora. Cada tipo de electrodoméstico dispondrá de un sistema específico que le permita realizar su función e interactuar con el usuario final.

**Automóviles:** El control eléctrico de los automóviles fabricados hoy en día es cada vez más complejo y precisa de numerosos dispositivos embebidos, para los sistemas de ignición, transmisión, frenado, suspensión, control de tracción, dirección asistida, seguridad, localización geográfica o control de emisiones. Un automóvil puede tener hasta un centenar de microprocesadores y microcontroladores, muchos de ellos comunicados entre sí.

**Máquinas de producción industrial:** En los procesos industriales, el control de motores, hornos, maquinaria, etc. Es manejado por sistemas embebidos, los cuales a menudo ofrecen una interfaz hombre-máquina para ser dirigidos por un operario e informarle al mismo de la marcha del proceso.

Videoconsolas: En muchos casos, este tipo de máquinas tienen más potencia de procesamiento que los PCs de su generación y su procesador está altamente

especializado para las demandas del tipo de videojuegos que va a permitir jugar. En ocasiones el diseño de cada procesador corre a cargo del propio fabricante de la videoconsola.

**Sistemas radar de aviones:** Los dispositivos para el procesado de la señal recibida o reflejada de los subsistemas radar embarcados en aviones requieren alta potencia de cálculo además de ocupar poco espacio, pesar poco y soportar condiciones extremas de funcionamiento (temperatura, presión atmosférica, vibraciones, etc.).

Así, se podría enumerar un sinfín más de ejemplos: teléfonos móviles, reproductores de audio o video, periféricos de una PC, navegadores GPS, controles remotos, equipos médicos, cajeros automáticos, máquinas expendedoras, etc.

#### 2.2.3 Características de los sistemas embebidos

Los sistemas embebidos poseen ciertas características que los distinguen de otros sistemas de cómputo, a continuación se describen las más importantes:

**Funcionamiento específico:** Un sistema embebido usualmente ejecuta un programa específico de forma repetitiva. Por ejemplo un *pager*, siempre es un pager. En contraste, un sistema de escritorio ejecuta una amplia variedad de programas, como hojas de cálculo, juegos, etc. Además nuevos programas son añadidos frecuentemente. Por supuesto puede haber excepciones, podría ocurrir que el programa del sistema embebido fuese actualizado a una nueva versión. Por ejemplo, un teléfono celular podría actualizarse de alguna manera.

Fuertes limitaciones: Todos los sistemas de computación poseen limitaciones en sus métricas de diseño, pero en los sistemas embebidos son muy fuertes. Una métrica de diseño es una medida de algunas características de implementación, como: costo, tamaño, desempeño, y consumo de energía. Los sistemas embebidos generalmente deben ser poco costosos, poseer un tamaño reducido, tener un buen desempeño para procesar datos en tiempo real, y además consumir un mínimo de energía para así extender el tiempo de vida de las baterías o prevenir la necesidad de elementos adicionales de enfriamiento.

Reactivos y tiempo real: Muchos sistemas embebidos deben ser reactivos o reaccionar ante cambios en el ambiente, además de realizar algunos cálculos en tiempo real sin ningún retraso, es decir, se deben tener resultados en tiempos fijos ante cualquier eventualidad. Por ejemplo, el módulo de control de viaje de un automóvil continuamente monitorea la velocidad y los sensores de frenos, reaccionando ante cualquier eventualidad. Ante un estímulo anormal, el módulo de

control debe realizar los cálculos de forma precisa y acelerada para garantizar la entrega de los resultados dentro de un tiempo límite, una violación en este tiempo podría ocasionar la pérdida del control del automóvil. En contraste, un sistema de escritorio se enfoca en realizar cálculos con una frecuencia no determinada y la demora de los mismos no produce fallas en el sistema.

Los sistemas embebidos resultan más flexibles y versátiles que los dispositivos diseñados totalmente por hardware, pero disponen de recursos más limitados que los sistemas de propósito general; estas limitaciones pueden afectar en mayor o menor medida sobre las características del producto final y depende de las especificaciones del problema y de la solución en concreto.

# 2.2.3.1 Arquitectura de los sistemas embebidos<sup>10</sup>

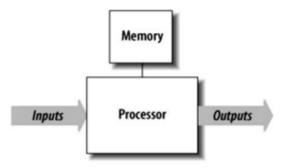

De manera general, un sistema embebido y una PC comparten una arquitectura semejante, tal y como está representada de forma sencilla en la Figura 1.

En la parte central se encuentra un microprocesador, un microcontrolador o un procesador digital se señal (DSP) que conforma la unidad central de proceso (CPU), es decir, la que aporta capacidad de cómputo al sistema, pudiendo incluir memoria interna o externa, o en principio cualquier arquitectura específica, según los requerimientos. Los subsistemas de memoria y de entrada/salida (E/S) se interconectan mediante los buses del sistema (compuestos a su vez por el bus de control, el bus de direcciones y el bus de datos).

El subsistema de entrada acepta datos del exterior para ser procesados mientras que el subsistema de salida transfiere los resultados hacia el exterior. Lo más habitual es que haya varios subsistemas de entrada y varios de salida. A estos subsistemas se les reconoce habitualmente como periféricos de E/S.

El subsistema de memoria almacena las instrucciones que controlan el funcionamiento del sistema. Estas instrucciones forman el programa que ejecuta el sistema. La memoria también almacena varios tipos de datos: datos de entrada que aún no han sido procesados, resultados intermedios del procesado y resultados finales en espera de salida al exterior.

28

<sup>&</sup>lt;sup>10</sup> Marcotegui Zabalza, Fernando. Representación de variables eléctricas en el sistema embebido Mini2440. 2011[En línea].

<sup>&</sup>lt; http://academica-e.unavarra.es/bitstream/handle/2454/4283/577623.pdf?sequence=1>

Figura 1. Esquema sencillo de una PC o de un sistema embebido

Fuente: Marcotegui Zabalza, Fernando. Representación de variables eléctricas en el sistema embebido Mini2440. [En línea].

< http://ac ademica-e.unavarra.es/bitstream/handle/2454/4283/577623.pdf?sequence=1>

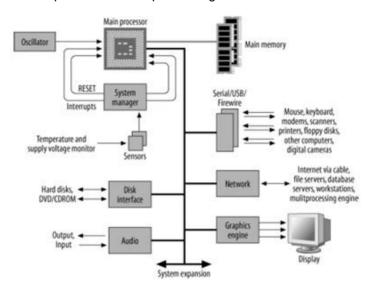

No obstante, como ya se ha comentado, las restricciones que presentan los sistemas embebidos hacen que su hardware presente una configuración diferente que las PCs, normalmente presenta menos recursos que estas últimas. Tomando como ejemplo la PC arbitraria representada en la Figura 2, la cual cuenta con una gran memoria principal para albergar al sistema operativo, aplicaciones y datos, y una interfaz para dispositivos de almacenamiento masivo (discos duros y DVD/CD-ROMs), posee además varios dispositivos de E/S para el usuario (teclado, ratón, micrófono, pantalla gráfica y audio) así como de conectividad (periféricos y red). El rápido procesador requerirá de un gestor del sistema para monitorizar la temperatura del núcleo y las tensiones de alimentación, así como para poder generar un *reset*.

Algunos tipos de sistemas embebidos, los de más alto rendimiento, pueden presentar un aspecto semejante a este. Por ejemplo, si funcionan como router o gateway, necesitarán una o varias interfaces de red, amplia memoria y alta velocidad de operación. Puede que también requieran algún tipo de interfaz de usuario como parte de su aplicación embebida, y en el caso extremo, simplemente son computadoras convencionales dedicadas a una tarea específica.

Sin embargo, dependiendo de las especificaciones que tengan que cumplir, los sistemas embebidos irán reduciendo los recursos disponibles.

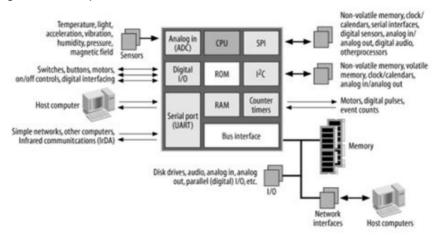

Los sistemas embebidos más pequeños utilizan microcontroladores como procesador, con la ventaja de que este procesador incorporara gran parte de las funcionalidades de la computadora en un solo chip.

En la Figura 3 se muestra un sistema embebido arbitrario basado en un microcontrolador genérico.

Figura 2. Diagrama de bloques de una computadora genérica

Fuente: Marcotegui Zabalza, Fernando. Representación de variables eléctricas en el sistema embebido Mini2440. [En línea].

< http://academica-e.unavarra.es/bitstream/handle/2454/4283/577623.pdf?sequence=1>

Figura 3. Diagrama de bloques de un sistema embebido arbitrario

Fuente: Marcotegui Zabalza, Fernando. Representación de variables eléctricas en el sistema embebido Mini2440. [En línea].

< http://academica-e.unavarra.es/bitstream/handle/2454/4283/577623.pdf?sequence=1>

Un microcontrolador es un circuito integrado que incluye una CPU, memoria y circuitos de E/S. Entre los subsistemas de E/S que incluyen los microcontroladores se encuentran los temporizadores, los conversores análogo-digital (ADC) y digital-análogo (DAC), así como también los canales de comunicación serial.

Estos subsistemas de E/S se suelen optimizar para aplicaciones específicas (por ejemplo audio, video, procesos industriales, comunicaciones, etc.) y se implementan dentro del microcontrolador como bloques de subsistemas.

A continuación se describen los elementos que con más frecuencia están presentes en las arquitecturas embebidas, aunque, como se ha comentado, pueden aparecer o no en un dispositivo en concreto. Estos elementos son muchas veces el objeto de las propias restricciones, siendo los más críticos el procesador y la memoria.

**Microprocesador:** Es el encargado de realizar las operaciones de cálculo principales del sistema y el que aporta capacidad de cómputo. Ejecuta código (conjunto de instrucciones) para realizar una determinada tarea y dirige el funcionamiento de los demás elementos que integran el sistema. La potencia de procesamiento se puede medir en términos del número de instrucciones que es capaz de ejecutar por unidad de tiempo, generalmente en MIPS (millones de instrucciones por segundo). Otra característica importante es el ancho de palabra del registro, que puede variar típicamente de 8 y 64 bits. Las PCs utilizadas hoy en día utilizan ya exclusivamente procesadores de 32 y 64 bits, sin embargo todavía es común en los sistemas embebidos utilizar procesadores más económicos de 8 o 16 bits.

Memoria RAM o principal: En ella se encuentra almacenado el código de los programas que el sistema puede ejecutar así como los datos. Su característica principal es que debe tener un acceso de lectura y escritura lo más rápido posible para que el microprocesador no pierda tiempo en tareas que no sean meramente de cálculo. Al ser volátil el sistema requiere de un soporte donde se almacenen los datos incluso sin disponer de alimentación o energía. La cantidad de memoria debe ser dimensionada correctamente por el diseñador y también puede afectar a la elección del procesador. En general, el ancho de palabra del registro del procesador establece el límite superior de la cantidad de memoria a la que pueda acceder. Por ejemplo, un registro de direcciones de 8 bits solo puede seleccionar una de entre 256 posiciones de memoria únicas.

**Cache:** Es una memoria más rápida que la principal en la que se almacenan los datos y el código accedido últimamente. Dado que el sistema realiza microtareas, muchas veces repetitivas, la caché permite ahorrar tiempo ya que no hará falta ir a memoria principal si el dato o la instrucción ya se encuentra en la caché. Dado su alto precio tiene un tamaño muy inferior con respecto a la principal. En el interior del chip de microprocesador se encuentra una pequeña caché, pero normalmente se tiene una mayor en otro chip de la placa madre.

**Disco Duro:** En él la información no es volátil y además puede conseguir capacidades muy elevadas. A diferencia de la memoria que es de estado sólido este suele ser magnético. Pero su exclusivo tamaño a veces lo hace no viable

para PCs embebidas, con lo que se requieren soluciones como unidades de estado sólido. Otro problema que presentan los dispositivos magnéticos, a la hora de integrarlos en sistemas embebidos, es que llevan partes mecánicas móviles, lo que los hace inadecuados para entornos donde estos estarán expuestos a ciertas condiciones de vibración. Existen en el mercado varias soluciones de esta clase (DiskOnChip, CompactFlash, IDE Flash Drive, etc.) con capacidades suficientes para la mayoría de sistemas embebidos (desde 2 MB hasta más de 1 GB).

BIOS-ROM (Basic Input & Output System-Read Only Memory): Memoria de solo lectura para el sistema básico de entrada y salida, es un chip de memoria específico para albergar un código fijo, necesario para inicializar la computadora y para poner en comunicación los distintos elementos de la placa madre. En muchos sistemas embebidos no existe tal memoria BIOS y el proceso de arranque lo realizan programas instalados en otro tipo de memorias, como por ejemplo Flash, a los que se conoce como bootloaders.

**CMOS-RAM:** Es un chip de memoria de lectura y escritura alimentado con una pila donde se almacena el tipo y ubicación de los dispositivos conectados a la placa madre (disco duro, puertos de entrada y salida, etc.). Además contiene un reloj en permanente funcionamiento que ofrece al sistema la fecha y la hora.

**Memoria Flash:** Es una tecnología de almacenamiento (derivada de la memoria E<sup>2</sup>PROM), que permite la lectura/escritura de múltiples posiciones de memoria en la misma operación. Existen dos tecnologías de memoria Flash (tipo NAND y tipo NOR, según el tipo de puertas lógicas utilizadas), cada una con sus características de densidad de almacenamiento, costo, velocidad de lectura/escritura/borrado, fiabilidad, etc.

**Chipset:** Chip que se encarga de controlar las interrupciones dirigidas al microprocesador, el acceso directo a memoria (DMA) y al bus ISA, además de ofrecer temporizadores y otras funcionalidades. Es frecuente encontrar la CMOS-RAM y el reloj de tiempo real en el interior del chip.

Periféricos de E/S: Los sistemas embebidos pueden tener una gran variedad de subsistemas de entrada/salida, tanto de control como de datos. Dependiendo de su función, pueden disponer de una o varias interfaces para interactuar con el usuario, tales como teclado, monitores, botones, dispositivos táctiles, etc. En otras ocasiones, sin embargo, su tarea se ejecuta en un segundo plano y su existencia puede no ser aparente para el usuario, como por ejemplo el sistema antibloqueo de frenos de un automóvil. Uno de los subsistemas de entrada/salida más comunes es el llamado general-purpose input-output (GPIO) que está basado en la lectura o escritura de valores digitales binarios en ciertos pines del circuito. Se puede utilizar para leer el estado de interrupciones, botones u otros dispositivos externos, o bien para activar o desactivar acciones, procesos, etc. Aunque la mayoría de los microcontroladores tienen otros subsistemas de E/S además de

GPIO, se suele proporcionar la posibilidad de convertir los otros subsistemas a GPIO si las funcionalidades de aquellos no son requeridas.

Muchos sistemas embebidos necesitan además entradas analógicas, por ejemplo procedentes de sensores de variables físicas, como temperatura, aceleración, presión acústica, intensidad lumínica, campo magnético, etc. para registrarlas, monitorizarlas o procesarlas. En tal caso el sistema deberá disponer también de un conversor ADC para digitalizar las señales.

Algunos sistemas embebidos disponen de puertos serie, que permiten la comunicación bien con una computadora anfitriona o *host*, con un modem (Figura 4), con otro sistema embebido o quizás acceder a una sencilla red. Existen formas especializadas de interfaces serie, tales como SPI e I<sup>2</sup>C, que permiten al procesador tener acceso a dispositivos periféricos tales como memorias externas, chips de reloj para sincronización, sensores digitales o analógicos u otros procesadores. Algunos sistemas embebidos también incluyen interfaces de red como Ethernet, USB o incluso *wireless*.

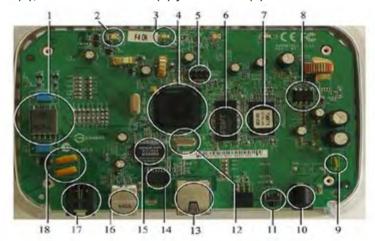

**Figura 4.** Componentes de un router/modem ADSL Natgear DG632. Las partes marcadas incluyen un microprocesador (4), una memoria RAM (6) y una Flash (7)

Fuente: Wikipedia. sistema embebido: Componentes de un router ADSL Natgear. [En Linea]. < http://es.wikipedia.org/wiki/Sistema\_embebido>

#### 2.2.3.2 Software en los sistemas embebidos

Como se mencionó en la sección 2.2.3.1, no existe una única arquitectura hardware para todos los dispositivos embebidos, sino que hay mucha variedad y flexibilidad en las configuraciones y cada una está condicionada por sus necesidades particulares. De la misma manera, el software que se ejecuta sobre los dispositivos no es el mismo para todos, sino que depende en

gran medida de la aplicación concreta, de la configuración hardware en particular, del número de capas que estén dando soporte por debajo a ese software, etc.

El concepto de software en el ámbito embebido es similar al del de las computadoras convencionales, aunque tiene ciertas peculiaridades que afectan a los programadores.

Básicamente, la idea que debería tener en mente una persona (con experiencia desarrollando aplicaciones para una PC) a la hora de desarrollar software embebido es que su ámbito de actuación va a estar ahora más cerca del hardware, tomando como referencia por ejemplo, el modelo de capas del sistema operativo osFree, mostrado en la Figura 5, significara que el programador va a trabajar más abajo en el diagrama, con menos capas de abstracción (librerías, interfaces de programación de aplicaciones (APIs), dependencias, etc.) en las que apoyarse. En definitiva, va a programar a más bajo nivel. Por otra parte, dado que los recursos son más limitados, el código debe hacer uso de ellos de forma especialmente eficiente. Como consecuencia, la programación se vuelve más específica para cada hardware, lo cual hace que las aplicaciones embebidas sean, en general, menos portables que en el mundo de las PCs.

OS/2 Process

OS/2 Process

OS/2 native application

os2app

os2app

os2serv

os2serv

os2fs

L4 Microkernel

Hardware

Figura 5. Arquitectura del sistema operativo OSfree

Fuente: Apesol. Arquitectura de sistema operativo OSFree: [En linea]. < http://stone-head.org/talks/2006/SENCICO-Soltech-SistemaOperativo\_Rudy.pdf >

**Sistemas operativos embebidos:** Se dan casos como el del reloj digital en los que la estructura es tan simple y las tareas a realizar son tan sencillas, que el desarrollo de software conlleva en sí mismo desde el nivel de aplicación hasta el sistema operativo, dando como producto una única imagen ejecutable que contiene todas las tareas para el sistema.

En otros casos en cambio, el software se ejecutara sobre una compleja estructura estratificada de librerías, APIs, dependencias, etc, tales como las aplicaciones para smartphones que tan de moda están hoy en día, Este software a su vez reposa sobre un sistema operativo, el cual toma una arquitectura adecuada al dispositivo.

El sistema operativo funciona de manera semejante al de una PC, gestionando los procesos básicos del sistema, aunque en este caso estará diseñado para ser más compacto y eficiente, y por tanto carecerá de algunas funcionalidades que ofrecen los sistemas operativos mayores.

Entre los dispositivos que cuentan con una estructura, la cual puede considerarse como un sistema operativo", destaca el conjunto de los mencionados smartphones, PDAs, tablets, teléfonos móviles convencionales y localizadores GPS.

Existen en el mercado varias empresas que están desarrollando sistemas operativos diferentes para este tipo de dispositivos a un nivel muy competitivo entre ellas, presentando diferentes filosofías tecnológicas y estrategias empresariales. En la Tabla 1 se muestra un resumen de algunos sistemas operativos embebidos vigentes hasta el año 2009.

**Tabla 1.** Sistemas operativos embebidos vigentes hasta el año 2009

| Nombre         | Gratuito | Código Abierto | Última<br>Actualización | Uso Principal                                       |

|----------------|----------|----------------|-------------------------|-----------------------------------------------------|

| VxWorks)       | No       | No             | Feb, 2009               | Modems,<br>Firewalls,<br>WirlessRouters             |

| QNX            | No       | No             | May, 2009               | Dispositivos de tiempo real                         |

| Windows CE     | No       | No             | Nov, 2007               | PDAs,<br>Smartphones                                |

| Windows Mobile | No       | No             | May, 2009               | PDAs,<br>Smartphones,<br>Dispositivos<br>multimedia |

| Ecos           | Si       | Si             | Mar, 2009               | Dispositivos de tiempo real                         |

| LynxOS         | No       | No             | Sep, 2006               | Aeronaves, automóviles                              |

| TinyOS         | No       | Si             | Ago, 2008               | Redes de<br>sensores,<br>motores                    |

| PalmOS         | No       | No             | Sep, 2006               | PDAs,<br>Smartphones                                |

| Garnet OS      | No       | No             | May, 2009               | PDAs,<br>Smartphones                                |

| Linux Embebido | Si | Si | Ago, 2006 | PDAs,<br>Smartphones,<br>WirlessRouters    |

|----------------|----|----|-----------|--------------------------------------------|

| Symbian        | No | No | Oct, 2008 | Smartphones                                |

| Inferno        | No | Si | Feb, 2007 | Sistemas<br>distribuidos de<br>tiempo real |

En cualquier caso, éste es un sector en auge y con buenas perspectivas de mercado. Esta cuestión se discutirá en mayor profundidad más adelante.

Lenguajes de programación: Como se ve, la programación embebida se hace a más bajo nivel, pero esto no significa que el programador tenga que descender todo el tiempo al lenguaje ensamblador. El lenguaje utilizado en la mayoría de las aplicaciones embebidas es C. Se trata de un lenguaje simple y relativamente fácil de aprender, que dispone de las estructuras típicas de los lenguajes de alto nivel pero que, a su vez, dispone de construcciones del lenguaje que permiten un control a muy bajo nivel.

Existen compiladores, prácticamente para cualquier procesador, que suelen ofrecer también, extensiones al lenguaje de programación utilizado, lo cual posibilita mezclar código en lenguaje ensamblador con código en lenguaje C o acceder directamente a memoria o dispositivos periféricos. En ocasiones, si la arquitectura así lo permite, es posible hacer una programación orientada a objetos en C++ o C#, aunque la programación embebida es tradicionalmente estructurada.

Otros lenguajes de programación que se vienen utilizando, sobre todo en los dispositivos que cuentan con una mayor capacidad para añadir nuevas capas, son Java, Pearl, Python, PHP, etc.

Sistemas en tiempo real: Una subclase especial dentro de los sistemas embebidos son los sistemas de tiempo real. Dentro de las especificaciones que deben cumplir estos sistemas, resulta crítico el tiempo de respuesta del sistema, debido a que un sistema de tiempo real debe responder dentro de un intervalo restringido de tiempo a eventos externos mediante la ejecución de la tarea asociada con cada evento.

Los sistemas de tiempo real se pueden caracterizar como blandos o duros. Si un sistema de tiempo real blando no cumple con sus restricciones de tiempo, simplemente se degrada el rendimiento del sistema, pero si el sistema es de tiempo real duro y no cumple con sus restricciones de tiempo, el sistema fallará, generando consecuencias catastróficas, por ejemplo en el caso del sistema de control del vuelo de un avión.

## 2.2.4 Historia y situación actual de los sistemas embebidos

Tal y como se definieron los sistemas embebidos en la sección 2.2.1, resulta imposible que hubieran podido existir antes de 1971, ya que fue en ese año cuando la compañía Norteamericana Intel lanzó al mercado el primer microprocesador de la historia, el 4004, diseñado para ser utilizado en una línea de calculadoras producida por la compañía japonesa Busicom.

Dos años antes, en 1969, Busicom había solicitado a Intel diseñar y fabricar un conjunto de circuitos integrados para una serie de modelos de calculadoras para negocios, de manera que cada calculadora tuviera su propio circuito específico.

Sin embargo, la propuesta de Intel fue diseñar un circuito de propósito general que pudiera ser utilizado en la línea entera de calculadoras. Este procesador de propósito general, el 4004, fue diseñado para leer y ejecutar un conjunto de instrucciones que estaban almacenadas como software en un chip externo de memoria. La idea de Intel era que sería el software lo que proporcionaría a cada calculadora su conjunto único de características.

Aquel microprocesador tuvo un éxito instantáneo y su uso creció progresivamente durante la siguiente década. Las primeras aplicaciones embebidas incluyeron pruebas espaciales no tripuladas, semáforos de tráfico computarizados y sistemas de control para la aviación.