# IMPLEMENTACIÓN DE REDES NEURONALES ARTIFICIALES EN HARDWARE RECONFIGURABLE.

FAUSTO MIGUEL CASTRO CAICEDO RIGO NELSON BENAVIDES CERÓN

UNIVERSIDAD DE NARIÑO FACULTAD DE INGENIERÍA PROGRAMA DE INGENIERÍA ELECTRÓNICA SAN JUAN DE PASTO 2010

# IMPLEMENTACIÓN DE REDES NEURONALES ARTIFICIALES EN HARDWARE RECONFIGURABLE.

## FAUSTO MIGUEL CASTRO CAICEDO RIGO NELSON BENAVIDES CERÓN

Trabajo de grado presentado como requisito parcial para optar el título de Ingeniero Electrónico

> Director del proyecto: Mg. JAIME ORLANDO RUIZ PAZOS Ingeniero Electrónico

UNIVERSIDAD DE NARIÑO FACULTAD DE INGENIERÍA PROGRAMA DE INGENIERÍA ELECTRÓNICA SAN JUAN DE PASTO 2010

"Las ideas y conclusiones aportadas en la tesis de grado, son responsabilidad exclusiva de los autores."

Artículo 1º. Acuerdo No. 324 de Octubre 11 de 1966, emanado del Honorable Consejo Directivo de la Universidad de Nariño

| Nota de Aceptación:             |

|---------------------------------|

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

| Firma del Presidente del Jurado |

|                                 |

|                                 |

|                                 |

|                                 |

| Firma del Jurado                |

|                                 |

|                                 |

|                                 |

| Firma del Jurado                |

#### **Dedicamos:**

A nuestros Padres que nos dieron la vida y han estado con nosotros en todo momento. Gracias por todo, por darnos una carrera para nuestro futuro y por creer en nosotros, aunque hemos pasado momentos difíciles siempre han estado apoyándonos y brindándonos todo su amor. Los queremos con todo el corazón y este trabajo, que nos llevó tiempo en culminar, es para ustedes, por ser los mejores padres del mundo.

A nuestros hermanos, sobrinos y seres queridos por estar con nosotros brindándonos todo su amor y apoyo incondicional.

A toda nuestra familia, quienes han sido un ejemplo de superación para poder alcanzar nuestras metas.

El verdadero sabio sólo es riguroso consigo mismo; con los demás es amable. PLUTARCO

#### **AGRADECIMIENTOS**

Expresamos nuestras más sinceras muestras de agradecimiento a:

Dios, por enseñarnos el camino correcto de la vida, guiándonos y fortaleciendo cada día nuestro espíritu.

Ing. Jaime Orlando Ruiz Pazos, director del trabajo de grado, por facilitarnos la principal herramienta para culminar este trabajo y por su permanente disposición desinteresada a la hora de guiarnos en distintas fases del proyecto.

Nuestros padres, Astheria Cerón, Rosalina Caicedo, Jonás Benavides, Rodrigo Castro, por su paciencia y por creer siempre en nosotros, apoyándonos en todas las etapas de nuestras vidas.

La Universidad de Nariño, por brindarnos la oportunidad de culminar nuestra carrera, que nos permite tener un futuro mejor.

Grupo de docentes del programa de Ingeniería Electrónica de la Universidad de Nariño, por sus consejos y por compartir con nosotros sus amplios conocimientos y experiencias.

Nuestros compañeros de estudio, por el apoyo que de ellos hemos recibido.

Los Autores.

#### RESUMEN

El propósito central del presente trabajo es la integración de las tecnologías FPGA y las Redes Neuronales Artificiales y surge como una alternativa para la creación de sistemas electrónicos complejos que se espera, contribuyan a resolver importantes problemas tecnológicos; tras esta perspectiva, se comienza por adquirir los componentes tanto teóricos como experimentales que permiten estimar y usar de manera eficiente los recursos de las tecnologías reconfigurables a la hora de implementar redes neuronales. Posteriormente se analiza un caso de estudio, el cual consiste en entrenar una red neuronal en software que determine cuando un tumor mamario es benigno o maligno. Finalmente, a partir de los conceptos adquiridos y los resultados logrados, la red neuronal obtenida se implementa en un FPGA Spartan 3 de la familia Xilinx haciendo uso del lenguaje de descripción de hardware VHDL.

Palabras Claves: Redes Neuronales, FPGA, VHDL.

#### **ABSTRACT**

The central aim of the present research is the integration of the technologies FPGA and the Artificial Neural Networks and it arises like an alternative for the creation of electronic complex systems and it's expected they contribute to solve important technological problems; according to this, firstly it's necessary to acquire the components so much theoretical as experimental that allow to estimate and to use in an efficient way the resources of configurable technologies when implementing neural networks. Later on a case of study is analyzed, which consists on training a neural network in software to determine when a breast tumor is benign or malicious. Finally, the neuronal network obtained is implemented in a Spartan 3 FPGA of the family Xilinx making use of the hardware description language VHDL.

Key Words: Neuronal Networks, FPGA, VHDL.

# CONTENIDO

|                                                          | Pág |

|----------------------------------------------------------|-----|

| INTRODUCCIÓN                                             | 21  |

| 1. MARCO CONCEPTUAL                                      | 22  |

| 1.1 REDES NEURONALES ARTIFICIALES (RNA)                  | 22  |

| 1.1.1 Estructura de un sistema neuronal artificial (ANS) | 23  |

| 1.1.2 Modos de operación de una red neuronal             | 24  |

| 1.1.2.1 Modo de entrenamiento                            | 24  |

| 1.1.3 Capacidad de generalización                        | 25  |

| 1.1.4 Patrones de entrenamiento                          | 26  |

| 1.1.4.1 Modo incremental                                 | 26  |

| 1.1.4.2 Modo batch                                       | 26  |

| 1.1.5 Clasificación de las redes neuronales artificiales | 26  |

| 1.1.5.1 Perceptrón                                       | 27  |

| 1.1.5.2 Adalina / Madalina                               | 28  |

| 1.1.5.3 Perceptrón multicapa (MLP)                       | 29  |

| 1.1.6 Algoritmo backpropagation                          | 31  |

| 1.2 LÓGICA RECONFIGURABLE                                | 31  |

| 1.2.1 Lenguajes de descripción de hardware (HDLs)        | 32  |

| 1.2.2 Codiseño hardware / software                       | 33  |

| 1.2.3 Dispositivos lógicos programables (PLDs)           | 33  |

| 1.3 FPGA (FIELD PROGRAMMABLE GATE ARRAY)                 | 34 |

|----------------------------------------------------------|----|

| 1.3.1 Programación de los FPGAs                          | 36 |

| 1.3.2 Evolución de los FPGAs                             | 36 |

| 1.3.2.1 FPGAs de Xilinx                                  | 37 |

| 2. ETAPA INVESTIGATIVA                                   | 39 |

| 2.1 DEFINICIÓN DEL MODELO MATEMÁTICO DE UNA RED NEURONAL | 39 |

| 2.1.1 Representación matricial de una neurona estándar   | 39 |

| 2.1.2 Representación matricial de una capa de neuronas   | 39 |

| 2.1.3 Representación matricial de redes multicapa        | 40 |

| 2.2 PARALELISMO EN REDES NEURONALES                      | 42 |

| 2.2.1 Paralelismo de capa                                | 42 |

| 2.2.2 Paralelismo de nodo                                | 42 |

| 2.2.3 Paralelismo de sinapsis                            | 42 |

| 2.2.4 Paralelismo sistémico                              | 43 |

| 2.3 ARITMÉTICA EN REDES NEURONALES                       | 43 |

| 2.3.1 Representación de datos                            | 43 |

| 2.3.1.1 Mínimo rango de precisión permitido              | 44 |

| 2.3.2 Procesamiento de suma de productos                 | 44 |

| 2.3.3 Funciones de activación                            | 45 |

| 2.3.3.1 Método por manejo de tablas                      | 45 |

| 2.3.3.2 Método por aproximaciones polinómicas            | 47 |

| 2.4 MODOS DE ENTRENAMIENTO DE LINA RED NEURONAL EN EPGA  | 48 |

| 2.4.1 Entrenamiento externo (offline learning)                          | 48 |

|-------------------------------------------------------------------------|----|

| 2.4.2 Entrenamiento interno (on-chip learning)                          | 48 |

| 2.5 BLOQUES BÁSICOS DE UNA RED NEURONAL                                 | 48 |

| 2.5.1 Módulos de entrada                                                | 49 |

| 2.5.2 Unidad de cómputo paralelo                                        | 49 |

| 2.5.2.1 Unidad de procesamiento PE                                      | 49 |

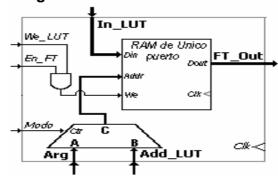

| 2.5.2.2 Módulo para la función de activación                            | 49 |

| 2.5.3 Interfaz                                                          | 49 |

| 2.5.4 Bloque algorítmico                                                | 50 |

| 2.5.5 Sistema de comunicaciones                                         | 50 |

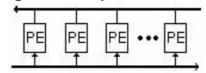

| 2.5.5.1 Arquitectura orientada a bus o BBA (broadcast bus architecture) | 50 |

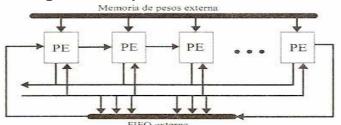

| 2.5.5.2 Arquitecturas sistólicas                                        | 51 |

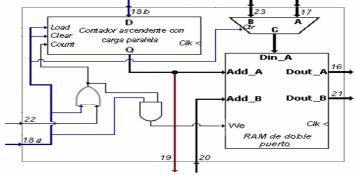

| 2.5.6 Unidad de almacenamiento                                          | 53 |

| 2.5.6.1 Memoria de almacenamiento distribuida                           | 53 |

| 2.5.6.2 Memoria de almacenamiento centralizada                          | 53 |

| 2.5.7 Módulos de salida                                                 | 53 |

| 2.5.8 Unidad de control                                                 | 54 |

| 2.5.8.1 SISD (single instruction, single data)                          | 54 |

| 2.5.8.2 SIMD (single instruction, multiple data)                        | 54 |

| 2.5.8.3 MISD (multiple instruction, single data)                        | 54 |

| 2.5.8.4 MIMD (multiple instruction, multiple data)                      | 54 |

| 3. ETAPA DE DISEÑO SOFTWARE                                             | 55 |

| 3.1 ESTUDIO Y PLANTEAMIENTO DE LA APLICACIÓN                   | 55 |

|----------------------------------------------------------------|----|

| 3.2 DISEÑO DE LA RED NEURONAL                                  | 56 |

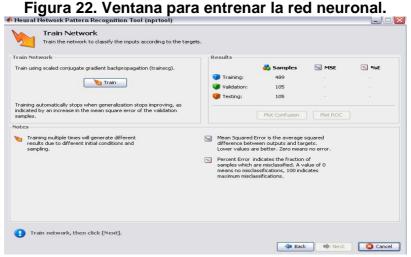

| 3.3 ENTRENAMIENTO SOFTWARE DE LA RED NEURONAL                  | 58 |

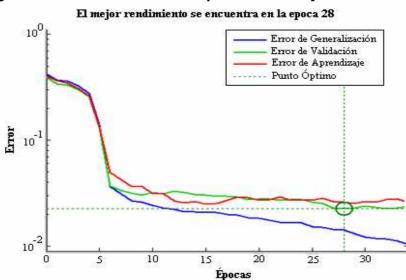

| 3.4 ANÁLISIS DE RESULTADOS DE LA ETAPA DE DISEÑO SOFTWARE      | 60 |

| 4. ETAPA DE DISEÑO HARDWARE                                    | 63 |

| 4.1 DISEÑO VHDL                                                | 63 |

| 4.1.1 Prototipos hardware                                      | 64 |

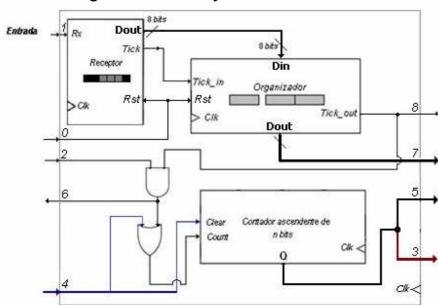

| 4.1.1.1 Prototipos combinacionales                             | 64 |

| 4.1.1.2 Prototipos secuenciales                                | 67 |

| 4.2 CARACTERÍSTICAS DEL SISTEMA                                | 72 |

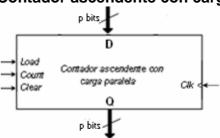

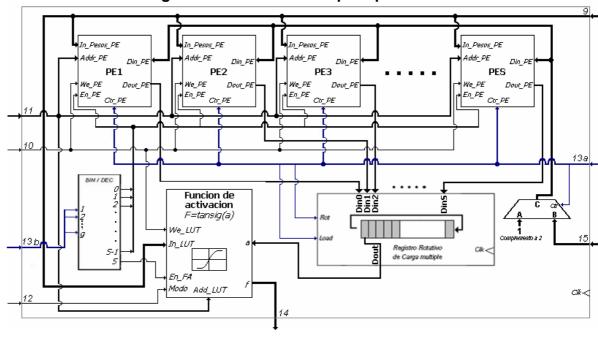

| 4.3 DISEÑO DEL SISTEMA NEURONAL ARTIFICIAL                     | 73 |

| 4.4 CONFORMACIÓN DE BLOQUES FUNCIONALES                        | 74 |

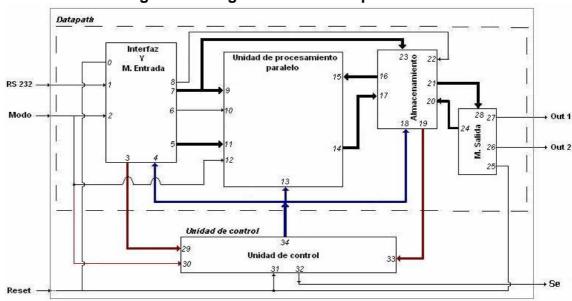

| 4.4.1 Interfaz y módulo de entrada                             | 74 |

| 4.4.2 Unidad de cómputo paralelo                               | 75 |

| 4.4.2.1 Funcionamiento interno de un procesador elemental (PE) | 76 |

| 4.4.2.2 Lógica de la función de activación                     | 78 |

| 4.4.2.3 Funcionamiento de la unidad de cómputo paralelo        | 79 |

| 4.4.2.4 Aspectos generales de la representación de datos       | 80 |

| 4.4.3 Sistema de comunicaciones                                | 81 |

| 4.4.4 Unidad de almacenamiento                                 | 81 |

| 4.4.5 Unidad de control                                        | 82 |

| 4.4.6 Módulo de salida                                         | 85 |

| 4.5 ANÁLISIS DE RESULTADOS DE LA ETAPA DE DISEÑO HARDWARE                    | 86 |

|------------------------------------------------------------------------------|----|

| 4.5.1 Análisis del desempeño de una red neuronal desarrollada en software co | n  |

| respecto a otra implementada en hardware reconfigurable                      | 87 |

| APORTE A FUTUROS TRABAJOS                                                    | 89 |

| CONCLUSIONES                                                                 | 90 |

| BIBLIOGRAFÍA                                                                 | 92 |

| NETGRAFÍA                                                                    | 94 |

| ANEXOS                                                                       | 95 |

# LISTA DE TABLAS

|                                                                  | Pág |

|------------------------------------------------------------------|-----|

| Tabla 1. Funciones de activación habituales.                     | 23  |

| Tabla 2. Familias de FPGAs de Xilinx.                            | 38  |

| Tabla 3. Clasificación según las salidas de la red.              | 57  |

| Tabla 4. Almacenamiento de los datos en la memoria ram de un PE. | 78  |

| Tabla 5. Instrucciones de control estáticas.                     | 83  |

| Tabla 6. Instrucciones de control dinámicas.                     | 83  |

| Tabla 7. Reporte final del proceso de síntesis.                  | 86  |

| Tabla 8. Comparación hardware reconfigurable frente a software.  | 88  |

| Tabla 9. Características de la familia spartan 3.                | 98  |

# LISTA DE FIGURAS

|                                                               | Pág. |

|---------------------------------------------------------------|------|

| Figura 1. Modelo de neurona estándar.                         | 23   |

| Figura 2. Estructura jerárquica de un sistema basado en RNA.  | 24   |

| Figura 3. Clasificación de las redes neuronales artificiales. | 27   |

| Figura 4. Arquitectura del perceptrón.                        | 27   |

| Figura 5. Arquitectura de una red adalina.                    | 29   |

| Figura 6. Regiones de decisión del MLP.                       | 30   |

| Figura 7. Arquitectura de un MLP de dos capas.                | 31   |

| Figura 8. Estructura básica de los FPGA.                      | 35   |

| Figura 9. Modelo matricial de una neurona estándar.           | 39   |

| Figura 10. Modelo matricial de una capa de neuronas.          | 40   |

| Figura 11. Modelo matricial de redes multicapa.               | 41   |

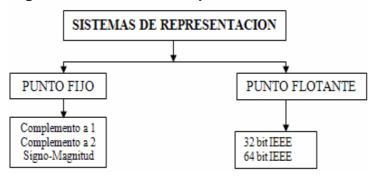

| Figura 12. Sistemas de representación de datos.               | 43   |

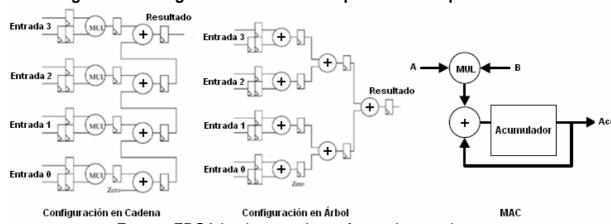

| Figura 13. Configuraciones habituales para suma de productos. | 45   |

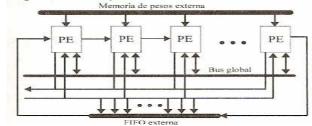

| Figura 14. Arquitectura BBA.                                  | 51   |

| Figura 15. Representación del Flujo de Datos.                 | 51   |

| Figura 16. Arquitectura sistólica SRA.                        | 52   |

| Figura 17. Arquitectura sistólica SRAGB.                      | 52   |

| Figura 19. Arquitectura de red.                               | 57   |

| Figura 20. Ventana para cargas datos de entrenamiento.        | 58   |

| Figura 21. Selección del número de neuronas de la capa oculta.                | 59       |

|-------------------------------------------------------------------------------|----------|

| Figura 22. Ventana para entrenar la red neuronal.                             | 59       |

| Figura 23. Progreso del entrenamiento de la RNA.                              | 61       |

| Figura 24. Evolución del error para los 3 conjuntos de datos.                 | 61       |

| Figura 25. Gráfica de la matriz de confusión.                                 | 62       |

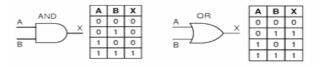

| Figura 26. Símbolo y Tabla de Verdad de la Puerta AND y OR.                   | 64       |

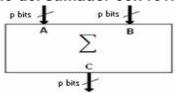

| Figura 27. Símbolo del sumador con revisión de overflow.                      | 65       |

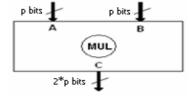

| Figura 28. Símbolo multiplicador paralelo.                                    | 65       |

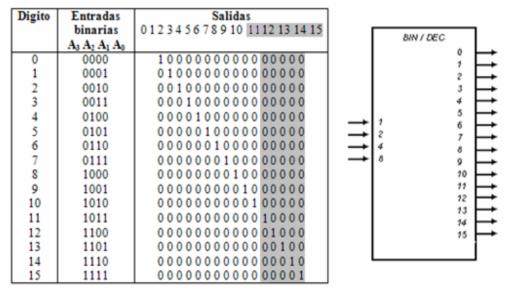

| Figura 29. Símbolo y tabla del mux de dos entradas de datos.                  | 66       |

| Figura 30. Símbolo y tabla de comportamiento para un decodificador binario de | <b>4</b> |

| bits.                                                                         | 67       |

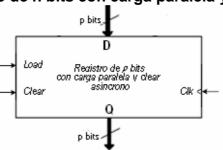

| Figura 31. Registro de n bits con carga paralela y clear asíncrono.           | 68       |

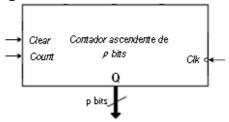

| Figura 32. Contador ascendente.                                               | 68       |

| Figura 33. Contador ascendente con carga paralela.                            | 69       |

| Figura 34. Ram de único y doble puerto.                                       | 69       |

| Figura 35. Diagrama del registro rotativo de carga múltiple.                  | 70       |

| Figura 36. Símbolo circuito UART.                                             | 71       |

| Figura 37. Símbolo circuito organizador.                                      | 72       |

| Figura 38. Diagrama del ANS implementado.                                     | 73       |

| Figura 39. Interfaz y módulo de entrada.                                      | 75       |

| Figura 40. Unidad de cómputo paralelo.                                        | 76       |

| Figura 41. Procesador elemental.                                              | 77       |

| Figura 42. Función de activación.                         | 78  |

|-----------------------------------------------------------|-----|

| Figura 43. Unidad de almacenamiento de datos intermedios. | 81  |

| Figura 44. Diagrama de flujo de la unidad de control.     | 84  |

| Figura 45. Visualización de resultados.                   | 86  |

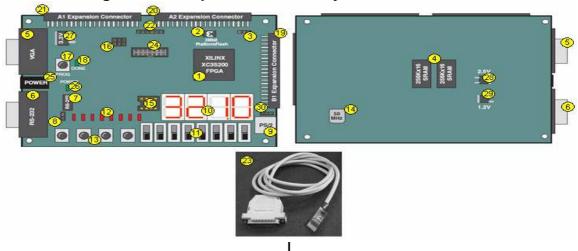

| Figura 46. Tarjeta de desarrollo S3.                      | 96  |

| Figura 47. Componentes de la tarjeta de desarrollo S3.    | 97  |

| Figura 48. Arquitectura de la spartan 3.                  | 99  |

| Figura 49. Ventana principal Ise 7.1                      | 102 |

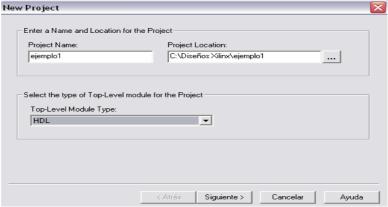

| Figura 50. Ventana para crear nuevo proyecto.             | 102 |

| Figura 51. Propiedades del dispositivo.                   | 103 |

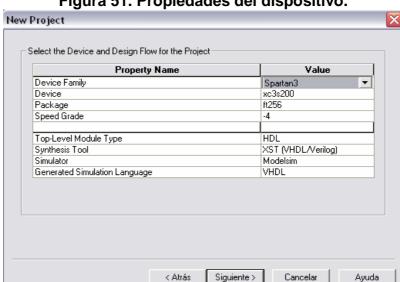

| Figura 52. Creación de un nuevo módulo VHDL.              | 104 |

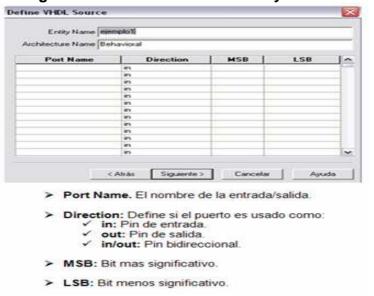

| Figura 53. Definición de entradas y salidas.              | 104 |

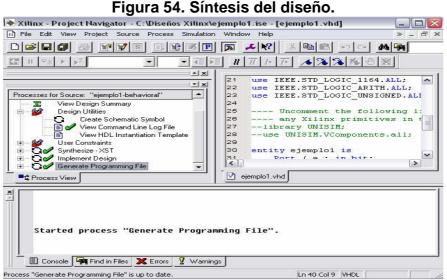

| Figura 54. Síntesis del diseño.                           | 105 |

# **LISTA DE ANEXOS**

|                                                      | Pág |

|------------------------------------------------------|-----|

| ANEXO A. PLATAFORMA DE DESARROLLO HARDWARE SPARTAN 3 | 96  |

| ANEXO B. FLUJO DE DISEÑO PARA FPGAs                  | 99  |

| ANEXO C. ISE WEB PACK 7.1                            | 101 |

#### **GLOSARIO**

ANS: Acrónimo para hacer referencia a un Sistema Neuronal Artificial (Artificial Neural Sistem).

BIAS: También llamado umbral, se considera como un peso adicional a la neurona al cual se le asocia una entrada permanente de valor 1 y se simboliza con la letra b.

BIOPSIA: Extirpación parcial del tejido para análisis y diagnóstico.

BIT: Unidad básica de información con la que trabajan los ordenadores. Puede tener dos estados (1,0).

BP: Backpropagation.

CLB: Bloque Lógico Configurable (Configurable Logic Block).

DESCRIPCIÓN COMPORTAMENTAL: Descripción de un sistema sin tener en cuenta el funcionamiento interno de este.

FPGA: Arreglo de Compuertas Programable por Campo (Field Programmable Gate Array).

FT: Función de transferencia o activación.

IOB: Input Output Block.

LUT: Look Up Table.

MAC: Unidades de multiplicación y acumulación.

MÁQUINAS VON NEUMANN: Son las clásicas máquinas de procesamiento secuencial.

MATLAB: Acrónimo de Matrix Laboratory. Lenguaje de programación para ingeniería desarrollado por MathWorks.

MLP: Perceptrón Multi Capa (Multi Layer Perceptron).

MODELSIM: Paquete computacional de la compañía Mentor Graphics que permite simular circuitos digitales descritos con HDLs.

NIBBLE: Grupo de 4 bits.

NPRTOOL: Comando de Matlab para acceder a bases de datos que permiten entrenar redes neuronales aplicables a reconocimiento de patrones.

PARALELISMO: El paralelismo de una red neuronal está directamente relacionado con el número de unidades de procesamiento que tiene la red.

PE: Procesador Elemental.

PESOS: Es un factor que se asocia a cada entrada de una neurona con el fin de excitarla o inhibirla y se simboliza con la letra W.

PIPELINING: Técnica utilizada en microprocesadores avanzados en la cual se comienza ejecutando una segunda instrucción antes que la primera haya sido finalizada.

PUERTO PARALELO. Punto de conexión de un ordenador que permite el traspaso de un grupo de bits a la vez.

PUERTO SERIAL: Punto de unión en el computador que hace posible el intercambio de bits (uno tras otro), con un equipo externo.

RED NEURONAL ARTIFICIAL: Son sistemas hardware o software de procesamiento que copian esquemáticamente la estructura neuronal del cerebro para tratar de reproducir sus capacidades y su acrónimo es RNA.

t: Valores objetivo de la red neuronal.

TAXONOMÍA DE FLYNN: Clasifica los sistemas digitales en 4 grupos dependiendo del flujo de datos y el flujo de instrucciones.

TOP DOWN: Metodología de diseño que parte de lo más general a lo más específico.

UART: Universal Asynchronous Receiver Transmitter. Es un componente del ordenador que maneja comunicaciones seriales asíncronas.

USB: Canal para el traspaso de datos universal.

VHDL: Lenguaje de descripción de Hardware de Alta Velocidad.

VLSI: Integración en escala muy grande.

## INTRODUCCIÓN

El uso de redes neuronales es muy apropiado para abordar tareas en las cuales la información se presenta masiva, imprecisa y distorsionada, hecho por el cual esta técnica viene siendo cada día más utilizada. Por lo general su implementación es realizada mediante simulación software. Esto implica el uso de un sistema basado en microprocesador; caracterizado por utilizar un esquema de computo puramente secuencial que impide que sea explotada la capacidad de cálculo masivamente paralelo inherente a este tipo de redes, lo anterior resulta claro si se tiene en cuenta que el poder de procesamiento de una red neuronal no radica en la utilización de un potente procesador capaz de ejecutar una serie de instrucciones (una tras otra) a alta velocidad y con un alto grado de precisión, sino en la utilización de un grupo de procesadores muy sencillos y poco precisos (llamados neuronas) trabajando al mismo tiempo, esta es la razón por la cual la realización hardware resulta ser la mas indicada para la implementación de redes neuronales.

La tecnología de implementación más habitual para la realización hardware de redes neuronales es la microelectrónica VLSI, en forma de ASIC. Ésta tecnología, se adapta muy bien a la implementación de sistemas paralelos, como es el caso de las redes neuronales. El diseño de ASIC es una alternativa computacionalmente muy potente, pero así mismo su realización requiere una considerable inversión tanto en dinero como en tiempo de diseño, con lo cual se hace injustificable para el desarrollo rápido y económico de prototipos o series pequeñas.

Actualmente, gracias al surgimiento de tecnologías como los FPGAs, con la capacidad de reconfigurar su estructura hardware, se abre una nueva posibilidad de realizar implementaciones hardware de redes neuronales. Los FPGA permiten la creación de sistemas complejos en un corto tiempo de diseño , y por sus características resultan atractivos para la creación de sistemas neuronales electrónicos, no sólo por el hecho de que están en la capacidad de brindar un alto grado de paralelismo sino también por la flexibilidad que poseen, estos son fácilmente programables por el usuario mediante herramientas CAD, que permiten captura esquemática, síntesis y simulación a partir de un HDL (lenguaje de descripción de hardware) y aunque en comparación con los ASICs, su velocidad y densidad de puertas es menor, estos brindan la posibilidad de poderse reconfigurar. En base a lo anterior es como surge la necesidad de realizar un esfuerzo investigativo que apunte a aprovechar eficientemente los recursos y características de estas tecnologías a la hora de implementar redes neuronales, y por ende que contribuya al mejoramiento de los sistemas electrónicos actuales.

#### 1. MARCO CONCEPTUAL

A lo largo de esta sección se exponen los conceptos fundamentales de la teoría de redes neuronales, especialmente los relacionados con la estructura de la neurona artificial, la arquitectura de red y modos de operación, enfocados hacia la solución de problemas prácticos. Posteriormente se describen las características principales que posee la Lógica Reconfigurable, profundizando en los dispositivos FPGA, lo cual permite que el lector comprenda las ventajas y desventajas que conlleva la utilización de estas tecnologías en la implementación de redes neuronales. Por último se termina con una breve perspectiva de la evolución de los FPGAs para generar una idea clara de la enorme potencia de procesamiento que tendrán en el futuro *las implementaciones de redes neuronales en hardware reconfigurable*.

## 1.1 REDES NEURONALES ARTIFICIALES (RNA)<sup>1</sup>

Las redes neuronales artificiales son sistemas de procesamiento inspirados en la estructura neuronal del cerebro para tratar de reproducir sus capacidades, los Sistemas Neuronales son capaces así de aprender de la experiencia a partir de las señales o datos provenientes del exterior. Su funcionamiento obedece a las siguientes reglas.

- 1. El procesamiento de información se lleva a cabo en muchos elementos simples con múltiples entradas y una única salida llamados neuronas (paralelismo de cálculo).

- 2. Las Neuronas envían señales entre ellas a través de un gran número de conexiones.

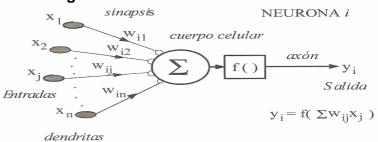

- 3. Cada conexión de una neurona i tiene asociado un factor que se multiplica con las señales de entrada  $(x_1, x_2, ..., x_n)$ , estos factores se denominan pesos  $(w_{i1}, w_{i2}, ..., w_{in})$ . Las señales resultantes pasan posteriormente al cuerpo celular (ver figura 1).

- 4. Cada neurona i obtiene su salida  $y_i$  aplicando una función de activación o transferencia (FT), a la suma de las señales que entran al cuerpo celular. Las principales funciones de activación son mostradas en la tabla 1.

<sup>&</sup>lt;sup>1</sup> SAMARASINGHE, Sandhya. Neural Networks for applied Sciences and engineering: from fundamental to complex pattern recognition. New York: Auerbach, 2006. p. 19.

Figura 1. Modelo de neurona estándar.

Fuente. Redes neuronales y sistemas borrosos.

Tabla 1. Funciones de activación habituales.

|                           | Función         | Rango   | Gráfica |

|---------------------------|-----------------|---------|---------|

| ldentidad<br>o<br>Purelin | y = k           | (-∞,+∞) |         |

| Escalon<br>o<br>Hardlims  | y = Hardlims(k) | [-1,+1] | *       |

| Sigmoidea<br>o<br>Tansig  | y=Tansig(k)     | (1,+1)  | , k     |

Fuente. Redes neuronales y sistemas borrosos.

- **1.1.1 Estructura de un sistema neuronal artificial (ANS)**<sup>2</sup>. El elemento más importante es la neurona (figura 1), el cual al agruparse con otras forman capas y a su vez la unión de varias capas constituye una red que junto con las interfaces de entrada y salida, más los módulos convencionales adicionales constituyen un sistema global. Un sistema neuronal está compuesto por los siguientes elementos (figura 2).

- Un Conjunto de Procesadores Elementales o Neuronas Artificiales.

- ➤ Un Patrón de Conectividad o Arquitectura. Puede ser de dos tipos, realimentado o unidireccional.

<sup>&</sup>lt;sup>2</sup> DEL BRÍO, Bonifacio Martín y SANZ MOLINA, Alfredo. Redes Neuronales y Sistemas Borrosos. 3<sup>ra</sup> ed. México: Alfaomega, 2007. p. 13.

- ➤ Una Regla o Dinámica de Aprendizaje. También llamado algoritmo de aprendizaje. Permite determinar los pesos de cada conexión durante el entrenamiento.

- > El Entorno Donde Opera.

- **1.1.2 Modos de operación de una red neuronal**<sup>3</sup>. Las RNA pueden trabajar en dos modos: modo de aprendizaje o entrenamiento y modo de recuerdo o ejecución.

- **1.1.2.1 Modo de entrenamiento.** Consiste en modificar los pesos sinápticos siguiendo una cierta regla de aprendizaje construida normalmente a partir del la optimización de una función de error, que mide la eficacia actual de la operación de la red.

Neurona Capa Red Sistema neuronal

Figura 2. Estructura jerárquica de un sistema basado en RNA.

Fuente. Redes neuronales y sistemas borrosos.

El anterior es un proceso iterativo que se repite una y otra vez hasta que la red alcanza el rendimiento deseado.

A continuación se presenta los tipos de entrenamiento más aplicados en redes neuronales.

#### • Entrenamiento supervisado.

La mayor parte de arquitecturas de RNA son entrenadas mediante métodos supervisados. En este tipo de entrenamiento, a la red neuronal se le presenta un

<sup>&</sup>lt;sup>3</sup> Ibíd., p 30.

conjunto de entradas junto con sus respectivas salidas deseadas u objetivos, e iterativamente ésta ajusta sus pesos hasta que su salida tiende a ser la deseada, utilizando para ello información detallada del error que se comete en cada paso. Una vez que el entrenamiento termina, los pesos se fijan en sus valores obtenidos.

### • Entrenamiento no supervisado.

A diferencia del aprendizaje supervisado, en el no supervisado no existe ningún maestro externo que indique si la red neuronal está operando correcta o incorrectamente. Así durante el entrenamiento, la red debe descubrir por sí misma, rasgos comunes, regularidades, correlaciones o categorías en los datos de entrada e incorporarlos en su estructura interna de conexiones (pesos). A este proceso se le llama auto-organización.

## Aprendizaje hibrido.

En este tipo de aprendizaje se hace uso de los dos tipos de aprendizaje anteriores los cuales tienen lugar normalmente en diferentes capas de la red.

### • Aprendizaje reforzado.

Es un tipo intermedio entre el aprendizaje supervisado y no supervisado, consiste en indicarle a la red únicamente si está actuando en forma correcta o incorrecta, sin brindar ningún detalle más. En ocasiones se denomina aprendizaje por premio o castigo.

- **1.1.2.2 Modo de recuerdo.** También llamado modo recuerdo (recall) o de ejecución Generalmente (aunque no en todos los modelos), una vez que el sistema ha sido entrenado, el aprendizaje se desconecta, por lo que los pesos y la estructura quedan fijos. Entonces se aplican nuevos datos de entrada con solución desconocida y se espera que la red esté preparada para dar una solución verdadera en base a lo aprendido durante el entrenamiento<sup>4</sup>.

- **1.1.3 Capacidad de generalización**<sup>5</sup>. Uno de los aspectos fundamentales de las RNA es su capacidad para generalizar. Por generalización se entiende la capacidad de la red de dar una respuesta correcta ante patrones que no han sido empleados en su entrenamiento. Una red neuronal bien entrenada generaliza, lo que significa que ha comprendido correctamente la mecánica del problema y no

-

<sup>&</sup>lt;sup>4</sup> [en línea] Disponible en Internet: http://eltamiz.com/elcedazo/2008/10/21/ inteligencia-artificial-redes-neuronales/

<sup>&</sup>lt;sup>5</sup> Ibíd., p. 75.

sólo los ejemplos concretos presentados. Hay que tener en cuenta que si se entrena una red hasta alcanzar un muy pequeño error de aprendizaje, la generalización se degrada. La explicación a esto es la siguiente; al principio la red se adapta progresivamente al conjunto de aprendizaje, acomodándose al problema y mejorando la generalización. Sin embargo, en un momento dado el sistema se ajusta demasiado a las particularidades de los patrones empleados en el entrenamiento, aprendiendo incluso el ruido entre ellos, cuando esto sucede se dice que hubo sobreaprendizaje o sobreajuste. Estos son dos aspectos que deben ser controlados adecuadamente para obtener un alto desempeño de red.

- **1.1.4 Patrones de entrenamiento**<sup>6</sup>. Supóngase una red de n entradas y S salidas, entonces un patrón de entrenamiento está conformado por el conjunto de entradas  $(x_1,x_2,...,x_n)$  y su respectivo conjunto de objetivos  $(t_1,t_2,...t_S)$  (salidas deseadas de la red). Durante el entrenamiento, el aprendizaje se lleva a cabo mediante la presentación sucesiva de un set de patrones de entrenamiento. Cuando todo este paquete de datos ingresa a la red, se dice que ha transcurrido una  $\acute{e}poca$ . Así, el proceso de aprendizaje se repite  $\acute{e}poca$  tras  $\acute{e}poca$  actualizando los pesos sinápticos hasta que se estabilicen en sus valores adecuados. Esta actualización es realizada generalmente, de dos formas:

- **1.1.4.1 Modo incremental.** Los pesos sinápticos son actualizados a medida que cada patrón de entrenamiento sea presentado a la red.

- **1.1.4.2 Modo batch.** Los pesos sinápticos se actualizan una vez haya entrado todo el conjunto completo de patrones de entrenamiento.

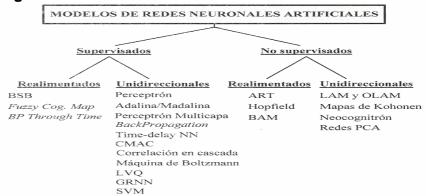

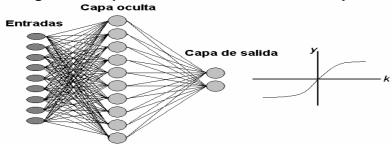

- **1.1.5 Clasificación de las redes neuronales artificiales**<sup>7</sup>. Las redes neuronales artificiales se clasifican de acuerdo a dos de sus características más notables: *tipo de aprendizaje*, y *arquitectura de la red* (figura 3). Para efectos de este documento, se describen sólo los tres modelos más conocidos y habituales en las aplicaciones prácticas, como lo son: el Perceptrón, la Adalina y el Perceptrón Multi-Capa, profundizando en este último, ya que es el utilizado para lograr el objetivo final del presente proyecto.

\_

<sup>&</sup>lt;sup>6</sup> HOWARD DEMUTH, Mark Beale y HAGAN, Martin. Matlab Neural Network Toolbox<sup>™</sup> 6 User's Guide, The Math Works Inc. 2009 [en línea] Disponible en Internet: (http://www.mathworks.com).

<sup>&</sup>lt;sup>7</sup> DEL BRÍO v SANZ MOLINA. Op. cit., p. 32.

Figura 3. Clasificación de las redes neuronales artificiales.

Fuente. Redes neuronales y sistemas borrosos.

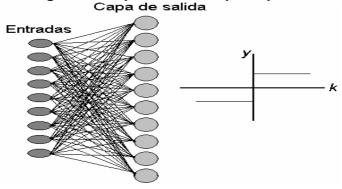

**1.1.5.1 Perceptrón**<sup>8</sup>. Este modelo tiene gran importancia histórica ya que fue el primero en poseer un mecanismo de entrenamiento que permite determinar automáticamente los pesos sinápticos que clasifican correctamente a un conjunto de patrones (linealmente separables) a partir de un conjunto de ejemplos. Estas redes consisten de una única capa de S neuronas conectadas a *n* entradas, como muestra la figura 4.

Figura 4. Arquitectura del perceptrón.

Un Perceptrón emplea principalmente dos funciones de transferencia (FT), *Hardlim* con salidas 1, 0 o *Hardlims* con salidas 1, -1; su uso depende del valor de salida que se espera, dando de esta manera, sólo salidas binarias. Una neurona con FT *Hardlim*, responde con 1 si el vector de entrada pertenece a la clase a la que representa y responde con 0 en caso contrario.

27

<sup>&</sup>lt;sup>8</sup> BERTONA, Luís Federico. Entrenamiento De Redes Neuronales Basado En Algoritmos Evolutivos. Tesis de grado. 2005. p. 12. (Ingeniero de sistemas) Universidad de Buenos Aires.

La salida de la red de la figura 4 está determinada por:

$$y_i = Hardlims(\sum_{j=1}^n w_{ij}x_j)$$

En ella, los sub-índices i,j indican que  $w_{i,j}$  es el peso de conexión entre la j-ésima entrada y la i-ésima neurona<sup>9</sup>.

El algoritmo de entrenamiento del perceptrón se encuentra dentro de los denominados algoritmos por corrección de errores. Este tipo de algoritmos ajustan los pesos de manera proporcional a la diferencia entre la salida actual proporcionada por la red y la salida objetivo, con el fin de minimizar el error producido por la red<sup>10.</sup>

**1.1.5.2** Adalina / Madalina<sup>11</sup>. Su nombre proviene de Adaptive Linear Network (Red Adaptativa Lineal). La topología de la red Adalina (figura 5), es similar a la del Perceptrón, solo que en este caso la FT es de tipo lineal (purelin).

La red Adalina presenta la misma limitación del Perceptrón, en cuanto al tipo de problemas que pueden resolver. Ambas redes pueden resolver únicamente problemas linealmente separables, pero ésta utiliza como método de aprendizaje, la regla de Widrow-Hoff, también conocida como regla LMS (Least Mean Squares, mínimos cuadrados), el cual es más potente que el utilizado en el Perceptrón. Este algoritmo de entrenamiento realiza una actualización continua de los pesos sinápticos de acuerdo con la contribución de cada neurona sobre el error total de la red.

Existe una versión multicapa de la Adalina, denominada Madalina (Multiple Adalina), que consiste en una red neuronal con neuronas similares a las de la Adalina pero que contiene capas de neuronas ocultas.

\_

<sup>&</sup>lt;sup>9</sup> HOWARD DEMUTH, Mark Beale y HAGAN, Martin. Matlab Neural Network Toolbox<sup>™</sup> 6 User's Guide, The Math Works Inc. 2009 [en línea] Disponible en Internet: (http://www.mathworks.com). P 108.

<sup>&</sup>lt;sup>10</sup> WIDROW Bernard y LEHR, Michael A. Neural networks: Perceptrón, Madaline, and Backpropagation. 2003. p. 68.

<sup>&</sup>lt;sup>11</sup> BERTONA, Op. cit. p.13.

Figura 5. Arquitectura de una red adalina.

La salida de la red está dada por:

$$y_i = Purelin(\sum_{j=1}^n w_{ij}x_j)$$

Al igual que el Perceptrón, la red Adalina es una red de aprendizaje supervisado que necesita conocer de antemano los valores asociados a cada entrada<sup>12</sup>.

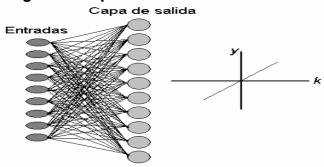

**1.1.5.3 Perceptrón multicapa (MLP)**<sup>13</sup>. Las Redes Perceptrón de una capa, mencionadas anteriormente, tienen una serie de limitaciones que les impiden realizar una gran variedad de aplicaciones, limitaciones que se pudieron solucionar con la inclusión de capas ocultas sobre estas redes, obteniendo de esta forma una red neuronal que se denomina Perceptrón Multicapa (MLP), que es quizá en la actualidad la red neuronal más utilizada.

Un Perceptrón multicapa es una red compuesta de varias capas de neuronas entre la entrada y la salida, dichas capas se unen de forma total hacia delante (feedforward), esto es, las entradas se unen con la primera capa y las salidas de ésta con la siguiente capa y así sucesivamente hasta la última capa (capa de salida).

Esta red permite establecer regiones de decisión mucho más complejas (figura 6), así por ejemplo para una arquitectura de Perceptrón de una capa, la región de decisión es una recta, mientras que el Perceptrón multicapa con una única capa de neuronas ocultas puede discriminar regiones convexas. Por otra parte, el

<sup>&</sup>lt;sup>12</sup> ACOSTA BUITRAGO, María Isabel y ZULUAGA MUÑOS, Camilo Alfonso. Tutorial sobre Redes Neuronales Aplicadas a Ingeniería Eléctrica y su Implementación en un Sitio Web. Colombia: Universidad Tecnológica de Pereira, 2000. p. 66.

<sup>&</sup>lt;sup>13</sup> lbíd., p. 63.

Perceptrón multicapa con dos capas de neuronas ocultas es capaz de discriminar regiones de forma arbitraria.

Figura 6. Regiones de decisión del MLP.

| Estructura | Regiones de<br>Decisión                                               | Problema<br>de la XOR | Clases con<br>Regiones<br>Mezcladas | Formas de<br>Regiones<br>más<br>Generales |

|------------|-----------------------------------------------------------------------|-----------------------|-------------------------------------|-------------------------------------------|

| 1 Capa     | Medio Plano<br>Limitado por<br>un Hiperplano                          | A B A                 | B                                   |                                           |

| 2 Capas    | Regiones<br>Cerradas o<br>Convexas                                    | B A B                 | B                                   |                                           |

| 3 Capas    | Complejidad<br>Arbitraria<br>Limitada por el<br>Número de<br>Neuronas |                       |                                     | 0                                         |

Fuente. Redes neuronales aplicadas en la ingeniería.

Para un correcto funcionamiento del MLP no es suficiente con realizar algunas modificaciones a la topología de la red, sino que se requiere de la elección de un buen método de aprendizaje como de la función de transferencia correcta; por lo general, se elije el algoritmo de aprendizaje supervisado Backpropagation (BP) y una función de transferencia diferenciable y no lineal como lo es la sigmoidea (tansig). La FT sigmoidea es utilizada en la mayoría de las redes MLP en sus capas ocultas, ya que le permite a los ANS aprender las variaciones no lineales de los distintos tipos de ambientes<sup>14</sup>.

La figura 7, muestra la arquitectura abreviada de un MLP. Tanto las neuronas de la capa oculta como las neuronas de la capa de salida usan como regla de propagación la suma ponderada de sus entradas con los pesos sinápticos y sobre esa suma ponderada se aplica una función de transferencia de tipo tansig, que es acotada en respuesta<sup>15</sup>.

<sup>&</sup>lt;sup>14</sup> HOWARD DEMUTH y HAGAN. Op. cit., p. 170.

<sup>&</sup>lt;sup>15</sup> DEL BRÍO y SANZ MOLINA. Op. cit., p. 63.

Figura 7. Arquitectura de un MLP de dos capas.

El modelo matemático de este tipo de redes, tiene gran importancia en el presente trabajo y se analiza más profundamente en la sección 2.1.

**1.1.6 Algoritmo backpropagation**<sup>16</sup>. Es el algoritmo de entrenamiento más utilizado en redes MLP. Es un método de aprendizaje supervisado de gradiente descendente, en el que se distinguen claramente dos fases. Primero se calcula la salida de la red para un patrón de entrada dado; esta salida se compara con la salida deseada, u objetivo, a partir de la cual se obtiene un error que determina la eficacia actual de la operación de la red. En la segunda fase se modifican los pesos en función de minimizar dicho error, mediante un procedimiento de propagación hacia atrás, este proceso se repite hasta cumplir con un criterio de parada (...)<sup>17</sup>.

Expuestos los fundamentos básicos de las redes neuronales, a continuación se procede a describir las herramientas relacionadas con su puesta en práctica en esta investigación, las cuales quedan enmarcadas dentro de la llamada lógica reconfigurable.

## 1.2 LÓGICA RECONFIGURABLE<sup>18</sup>

La lógica reconfigurable, es un escenario del diseño digital que coloca a disposición de los diseñadores herramientas de tipo software y hardware para la realización de aplicaciones mucho más robustas en menor tiempo y a menores costos. Involucra un paradigma de diseño basado en metodologías software, que

<sup>&</sup>lt;sup>16</sup> BERTONA. Op. cit., p 19.

<sup>&</sup>lt;sup>17</sup> FREEMAN James y SKAPURA, David M. Neural Networks Algorithms, Applications, and Programming Techniques. Wokingham: Addison-Wesley, 1991.

<sup>&</sup>lt;sup>18</sup> HERNANDEZ PEREZ, Alberto. Introducción al Lenguaje de Descripción de Hardware VHDL. Cuba: Centro de Investigaciones en Microelectrónica, CUJAE, 2004. p. 12.

conduce a una categoría de abstracción superior (Hardware), y que permite simplificar los procesos de verificación mediante la simulación.

Entre los dispositivos hardware y las herramientas software que hacen parte de la lógica reconfigurable se puede mencionar:

- Lenguajes de descripción de hardware (HDL).

- Codiseño hardware/software.

- Dispositivos programables.

**1.2.1 Lenguajes de descripción de hardware (HDLs).** Un lenguaje de descripción de hardware (HDL) es una herramienta que sirve para describir el comportamiento y la arquitectura de un circuito o sistema electrónico. Al utilizar un HDL para modelar un sistema, es importante recordar que se está modelando hardware, y no escribiendo software.

Los HDLs permiten describir la concurrencia y paralelismo que posee un sistema hardware (muchas cosas y muchas señales cambian al mismo tiempo). En dichos sistemas el tiempo es una variable importante; un cambio en el tiempo de propagación de una compuerta, el retardo de una traza en una plaqueta, o el no cumplir con los tiempos de establecimiento de un circuito, puede cambiar de manera radical el comportamiento del sistema digital que se esté realizando.

Usando HDLs, los sistemas digitales pueden describirse a diferentes niveles de abstracción. Estos modelos pueden ir desde el nivel abstracto del comportamiento general de un circuito hasta el nivel de interconexión de compuertas lógicas.

Uno de los aspectos interesantes de los HDLs es que permiten utilizar módulos ya creados, en nuevos diseños, lo que permite, por ejemplo, realizar conexiones en cascada, facilitando y optimizando el diseño<sup>19.</sup>

Aunque hay muchos lenguajes de descripción de hardware, dos predominan actualmente en el mundo del desarrollo digital: Verilog y VHDL. Existen otros, desarrollados por los distintos proveedores de herramientas o PLD, pero en la actualidad casi todos los fabricantes de PLD y proveedores de herramientas de desarrollo proveen soporte para VHDL y Verilog<sup>20</sup>.

<sup>&</sup>lt;sup>19</sup> ARMSTRONG, J R y GRAY, F G. Structure Logic Desing with VHDL. London England: Prentice Hall, 1993. p. 103.

<sup>&</sup>lt;sup>20</sup> ASHENDEN, Peter J. The Designer's Guide to VHDL. 2<sup>da</sup> ed. Morgan Kaufman, 2002. p. 256.

**1.2.2 Codiseño hardware / software**<sup>21</sup>. El término de codiseño Hardware / software es relativamente reciente, de principios de la década de los 90. Este término describe la confluencia de dos problemas en el diseño de circuitos integrados. Por una parte, está la arquitectura hardware y todas las tecnologías disponibles para su implementación y por otra, el diseño software que involucra los sistemas operativos, los lenguajes de programación, compiladores, herramientas de modelado, simulación y evaluación.

Con esta técnica es posible dividir las tareas a realizar (particionado hardware/software) de manera que parte de ellas son implementadas mediante un hardware de propósito específico y otras mediante la programación de un microprocesador de propósito general<sup>22</sup>. De tal forma que las tareas más críticas se implementan en hardware mientras que aquellas que se adaptan mejor a la ejecución de un microprocesador y en las que se requiere mayor flexibilidad se programan en software.

1.2.3 Dispositivos lógicos programables (PLDs). Son dispositivos de propósito general que contienen circuitos lógicos que se pueden programar. En la actualidad representan a uno de los sectores que más rápido crecimiento experimenta en la industria de los semiconductores debido a que permiten la creación de sistemas mucho más complejos en comparación con los sistemas creados mediante la actual lógica discreta.

La fabricación de dispositivos de lógica programable se fundamenta en el hecho de que cualquier función lógica se puede crear mediante una suma de productos (funcionalidad completa) y en el empleo de bloques lógicos que almacenan los datos de salida del circuito en lugar de implementar físicamente su ecuación booleana (celdas de funciones universales)<sup>23</sup>.

Las características principales de los PLDs son:

- Dispositivos con diversos recursos lógicos incorporados.

- Configurables por el usuario.

<sup>&</sup>lt;sup>21</sup> LAPLANTE, P. Real-time systems design and analysis. An engineer's handbook. IEEE Press: 1992. p. 198.

<sup>&</sup>lt;sup>22</sup> MAGDALENO, E.; RODRÍGUEZ, M.; AYALA, A.; MENDOZA, B. y RODRÍGUEZ, S. Metodología para el Aprendizaje de Sistemas Electrónicos Digitales y su Diseño. Bogotá: TAEE, 2004. p. 205.

<sup>&</sup>lt;sup>23</sup> [en línea] Disponible en Internet: http://gemini.udistrital.edu.co/ comunidad/ profesores/jruiz/jairocd

- Poseen Interconexiones programables.

- > Requieren herramientas CAD.

Los dispositivos lógicos programables (PLDs) forman parte de los circuitos de alto nivel de integración, que incluyen, entre otros, los PLDs simples (SPLDs), los PLDs complejos (CPLDs) y los arreglos de compuertas programables por campo (FPGAs). Por su importancia en esta investigación los últimos se abordan en forma más profunda a continuación.

# 1.3 FPGA<sup>24</sup> (FIELD PROGRAMMABLE GATE ARRAY)

Un FPGA es un arreglo de bloques lógicos, colocados en una infraestructura de interconexiones programables, fueron introducidos por Xilinx en 1985 y hoy en día son el dispositivo programable por usuario de más amplio espectro de aplicación. Es posible programar la funcionalidad de sus bloques lógicos, las interconexiones entre bloques y las conexiones entre entradas y salidas. Representan uno de los últimos avances en tecnología PLDs; algo muy importante de estos dispositivos es que se reconfiguran con un programa, a diferencia de lo que normalmente se conoce como sistema programado (microcontrolador, microprocesador etc), en donde un hardware fijo es capaz de interpretar y ejecutar un algoritmo, en los FPGA lo que se tiene es un hardware que se configura realizando conexiones físicas que son especificadas por un programa o cadena de configuración.

Estos dispositivos poseen características que los hacen atractivos para la implementación de redes neuronales, puesto que son capaces de brindar el paralelismo requerido, vienen dotados de altas capacidades en memoria y con bloques aritméticos dedicados; además su reconfigurabilidad puede ser aprovechada para optimizar operaciones de multiplicación por medio de tablas de búsqueda internas LUTs (look-up tables). No obstante debe aclararse que las redes neuronales debido a las númerosas conexiones y operaciones que realizan internamente consumen un elevado número de recursos hardware en el FPGA. Hace algunos años esto fue un limitante importante que causaba que los FPGAs sean inaplicables en la solución de problemas complejos mediante redes neuronales. Dicha limitación está siendo superada gracias a los permanentes avances en tecnología microelectrónica que permiten integrar millones de puertas en un pequeño chip.

\_

<sup>&</sup>lt;sup>24</sup> GÜICHAL, Guillermo. Diseño Digital Usando Lógica Programable. México: Universidad Tecnológica Nacional Facultad Regional Bahía Blanca, 2005. p. 47.

Los elementos básicos constituyentes de un FPGA se pueden ver en la figura 8 y son los siguientes:

- ➤ Bloques lógicos configurables (CLBs): Estos son los bloques básicos que se utilizan en la implementación de un circuito digital. Cada CLB contiene circuitos que le permiten realizar operaciones aritméticas eficientes y en forma concurrente (lo que convierte a los FPGAs en herramientas verdaderamente óptimas para la implementación de redes neuronales).

- ➤ Bloques de entrada salida (IOBs): Estos bloques proveen la interface entre los "pines" del integrado y la lógica interna.

- ➤ Recursos de interconexión: Es una estructura versátil y multi-nivel de interconexión entre los otros componentes de la FPGA.

Bioque Lógico Cétula E/S

Figura 8. Estructura básica de los FPGA.

Fuente. Diseño digital usando lógica programable.

El proceso de programación no es único, sino que se puede realizar mediante diferentes tecnologías, como son células RAM estáticas, transistores, memorias EPROM y EEPROM, etc. En el caso de las FPGAs de XILINX los elementos de programación se basan en células de memoria RAM que controlan transistores de paso, puertas de transmisión o multiplexores.

Los FPGAs permiten realizar una gran cantidad de aplicaciones y en muy diversas áreas, sobre todo en aquellas que requieren un alto grado de paralelismo. Entre éstas se tienen el procesamiento digital de señales, radio definido por software, sistemas aeroespaciales y de defensa, prototipos de ASICs, sistemas de imágenes para medicina, sistemas de visión para computadoras, reconocimiento de voz, bio-informática, emulación de hardware en computadora, entre otras.

**1.3.1 Programación de los FPGAs.** La tarea del programador es definir la función lógica que realiza cada uno de los *CLB*s, seleccionar el modo de trabajo de cada *IOB* e interconectarlos.

El diseñador cuenta con la ayuda de *entornos de desarrollo* especializados en el diseño de sistemas a implementarse en FPGA. Un diseño puede ser capturado ya sea como esquemático, o haciendo uso de un lenguaje de descripción de hardware (HDL). Los HDLs más utilizados son VHDL y Verilog<sup>25</sup>.

**1.3.2 Evolución de los FPGAs.** Pocos campos de la ciencia han avanzado de una forma tan vertiginosa como lo ha hecho la Electrónica, siendo sobre todo más evidente en lo que al diseño digital se refiere. Entre esos avances digitales se encuentra la tecnología FPGA.

El número de recursos internos de los FPGAs ha crecido notablemente en los últimos años, generándose dispositivos cada vez más preparados para distintas aplicaciones. Gracias a ello, es posible que estos dispositivos hayan pasado de ser usados inicialmente como elementos coprocesadores, a ser una poderosa plataforma tecnológica sobre la cual funcionan complejos sistemas de respuesta en tiempo real. Esto ha sido debido principalmente a las mejoras producidas en los procesos de fabricación de circuitos integrados y a la mejora del software de síntesis e implementación.

La mejora en los dispositivos reconfigurables ha posibilitado la implementación de sistemas digitales de alto nivel, comúnmente denominados como SOC (*System On Chip*), con un ahorro tanto económico como en tiempo de diseño. Económico porque el número de circuitos integrados se reduce al poder integrar en un FPGA númerosos sistemas digitales. Si el análisis se realiza desde un punto de vista de tiempo de diseño, los tiempos de elaboración de un proyecto también se reducen al integrar todo en un FPGA.

Uno de los principales problemas al que se enfrentan las personas que trabajan con FPGAs es cual escoger, ya que existen varios fabricantes que disponen de diversas ventajas. Los diseñadores coinciden en afirmar que existen tres fabricantes mayoritarios en la distribución de FPGAs y software de soporte: Xilinx, Altera y Actel. En el mercado mundial se pueden encontrar otros tantos con producciones menores pero que figuran también como FPGAs útiles: Lucent, Texas Instruments, Philips, QuickLogic, Cypress, Atmel, etc. El siguiente apartado se enfoca a los FPGAs de Xilinx, ya que el dispositivo utilizado en este proyecto pertenece a éste fabricante; además se da una breve introducción a las diferentes

\_

<sup>&</sup>lt;sup>25</sup> BASIL, M y SUARDÍAZ MURO, Juan. Nuevas Tendencias En El Diseño Electrónico Digital. Madrid España: Codiseño Hardware/Software, Universidad Alfonso X El Sabio, 2007. p. 98.

familias lógicas y a sus principales características, para así poder dar una idea clara de cuáles son los FPGAs más avanzados que tiene Xilinx en la actualidad<sup>26</sup>.

**1.3.2.1 FPGAs de Xilinx**<sup>27</sup>. Xilinx está considerado como líder entre los fabricantes de FPGAs a nivel mundial. Sus FPGAs están basados en la tecnología SRAM. Sus principales familias son: *XC3000, XC4000, XC Virtex, y XC Spartan*. La serie *XC Virtex*, o tan solo *Virtex*, es la más nueva de todas las familias de Xilinx. Se dice que los dispositivos pertenecientes a esta familia son los más rápidos (velocidades de trabajo de hasta 250 Mhz), densos en compuertas y menor consumo de potencia, pero por lo mismo son los más costosos.

La serie *Spartan* surgió como una opción para sustituir diseños probados de menos de 15.000 compuertas por dispositivos de bajo costo y alto desempeño, aunque llegan hasta aproximadamente 5 millones de puertas. Las series estándar *XC3000* y su sucesora, la *4000*, muestran la mayor parte de las características funcionales de los FPGAs de Xilinx, pero con la gran desventaja que son dispositivos de baja densidad de puertas, por lo cual son utilizadas para realizar prototipos de bajo impacto. La tabla 2 ilustra una breve comparación entre las familias de FPGAs de Xilinx.

<sup>&</sup>lt;sup>26</sup> Ibíd., p. 120.

<sup>&</sup>lt;sup>27</sup> HERRERA LOZADA, Juan Carlos. México: Tecnologías Programables, 2007. p. 29.

Tabla 2. Familias de FPGAs de Xilinx.

| Familia            | Año de creación | Número máx. de<br>puertas | Novedades                           |

|--------------------|-----------------|---------------------------|-------------------------------------|

| XC2000             | 1985            | 1800                      | Configuración SRAM                  |

| XC3000             | 1987            | 7500                      | Mayor número de<br>puertas          |

| XC4000/ Spartan    | 1991            | 180000                    | Memoria RAM                         |

| Virtex/ Spartan II | 1998            | 3M2/600K                  | BRAMs, DLLs                         |

| Virtex II          | 2000            | 8 M                       | DCMs.<br>Multiplicadores            |

| Spartan 3          | 2003            | 5 M                       | Bajo Coste                          |

| Virtex II-Pro      | 2002            | 4 M                       | Power PC, Rocket<br>I/O             |

| Virtex 4           | 2005            | 8 M                       | Ethernet MACs, DSP<br>Slice         |

| Virtex 5           | 2006            | 11 M                      | DSP Slice Avanzada,<br>BRAM 32KBits |

Fuente. Arquitectura basada en FPGA, para la detección de objetos.

### 2. ETAPA INVESTIGATIVA

Para implementar un sistema neuronal en hardware es necesario primeramente adquirir algunos conceptos básicos que permitan definir sus principales características, por tanto en esta etapa del proyecto se discuten temas relacionados con el modelo matemático, tipos de paralelismo, manejo de la aritmética interna, modos de entrenamiento y bloques básicos de un sistema neuronal.

# 2.1 DEFINICIÓN DEL MODELO MATEMÁTICO DE UNA RED NEURONAL<sup>28</sup>.

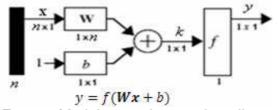

**2.1.1 Representación matricial de una neurona estándar.** Matricialmente, la salida y de una neurona estándar se puede modelar por medio de una función de activación f, que tiene como argumento k, la multiplicación de un vector de entrada  $\mathbf{x}$  (vector columna compuesto por n elementos,  $x_1, x_2, x_3...x_n$ ), por una matriz de pesos  $\mathbf{W}$  (compuesta por los pesos  $w_{11}, w_{12}, w_1...w_{1n}$ ), más un parámetro adicional denominado Bias o Umbral (puede considerarse como un peso adicional, al cual se le asocia permanentemente una entrada de valor 1), ver figura 9.

Figura 9. Modelo matricial de una neurona estándar.

Fuente. Matlab neural network toolbox.

Nótese que en esta representación la matriz **W** tiene un único renglón, debido a que se está representando una única neurona.

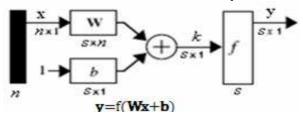

**2.1.2 Representación matricial de una capa de neuronas.** En base a la representación anterior, de neurona estándar, una capa de S neuronas puede ser representada como se muestra en la figura 10.

-

<sup>&</sup>lt;sup>28</sup> HOWARD DEMUTH, y HAGAN. Op. cit., p. 90.

Figura 10. Modelo matricial de una capa de neuronas.

Fuente. Matlab neural network toolbox.

#### Donde:

**x**, es un vector de entrada de *n* elementos.

W, es la matriz de pesos.

**b**, es el vector que contiene los Bias de cada neurona.

y, es la salida de S elementos.

Cabe destacar que la única diferencia entre representación de una neurona estándar y una capa de neuronas, es el tamaño de la matriz **W** y el vector **b**, ya que cada renglón de la matriz **W** representa el conjunto de pesos para cada neurona en la capa y cada elemento del vector **b** contiene el respectivo Bias de las neuronas.

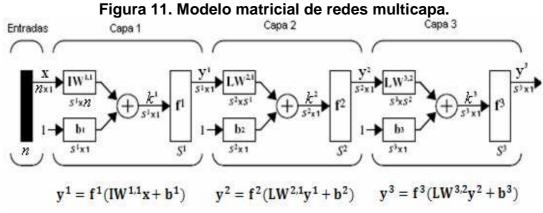

**2.1.3 Representación matricial de redes multicapa.** Para describir redes que poseen varias capas, se debe extender la notación hasta ahora utilizada, es necesario primero, hacer una distinción entre las matrices de pesos conectadas a las entradas y las matrices de pesos conectadas entre capas, y segundo, identificar el origen y el destino de las señales que entran a dichas capas.

Las matrices de pesos conectadas a la entrada de la red son llamadas *Pesos de Entrada* **IW** y las matrices de pesos conectadas a las salidas de otras capas son llamadas *pesos de capa* **LW**. Se utilizan superíndices para indicar el origen (segundo índice) y el destino (primer índice) de las señales que entran a las matrices de pesos.

En la figura 11, se muestra una red neuronal de tres capas, haciendo uso de la notación extendida, anteriormente mencionada.

Cada capa tiene asociado una matriz de pesos  $\mathbf{W}$ , un vector columna  $\mathbf{b}$ , y un vector columna de salida  $\mathbf{y}$ . Para distinguir entre el vector de pesos, vectores de salida, etc, de cada una de las capas, se utiliza un superíndice en la variable de interés.

Fuente. Matlab neural network toolbox.

La red mostrada arriba tiene n entradas,  $S^1$  neuronas en la primera capa,  $S^2$  neuronas en la segunda capa y  $S^3$  neuronas en la tercera capa. Nótese que las salidas de cada capa intermedia son las entradas a la siguiente capa, así la capa 2 puede ser analizada como una red de una capa con  $S^1$  entradas,  $S^2$  neuronas y una matriz de pesos  $LW^{2,1}$  de  $S^1xS^2$  elementos. La entrada a la capa 2 es  $y^1$  y la salida es  $y^2$ . Ahora que todos los elementos de la capa 2 han sido identificados ésta puede ser tratada como una red de una única capa de neuronas, en la figura 11, se puede observar las ecuaciones para cada una de las capas, (esta metodología puede ser aplicada a cualquier tipo de red).

Con lo mencionado hasta el momento, se puede definir matemáticamente la red neuronal de la figura 11, como sigue.

$$y^2 = f^2(LW^{3,2}f^2(LW^{2,1}f^1(IW^{1,1}x + b^1) + b^2)b^3)$$

Las capas que producen la salida de una red son llamadas capas de salida, y las demás son llamas capas ocultas. Aunque aquí no sea considerado así, se debe resaltar que algunos autores consideran al vector de entrada como una capa mas, la cual es llamada capa de entrada.

Habiendo definido la representación matemática que modela a una red neuronal se procede a discutir algunos aspectos relacionados con su implementación. Estos son necesarios para hacer un uso adecuado de los recursos hardware que poseen las tecnologías reconfigurables.

# 2.2 PARALELISMO EN REDES NEURONALES<sup>29</sup>

Los altos requerimientos computacionales de las tareas para las cuales está indicado el uso de redes neuronales, hacen que las arquitecturas Von Neumann (en las cuales se basan los sistemas digitales convencionales) no sean muy apropiadas, por ello la introducción de sistemas de cálculo paralelo resulta necesaria si se quiere lograr respuestas en tiempo real. De lo anterior se desprende el concepto de paralelismo. El paralelismo en una red neuronal está directamente relacionado con el número de unidades de proceso presentes en la red (también denominadas, *procesadores elementales o PEs*), los cuales son elementos secuenciales de la arquitectura encargados de realizar las operaciones aritméticas.

Las redes neuronales pueden ser desarrolladas en un FPGA a diferentes niveles de paralelismo, analizar cada uno de estos, resulta de gran importancia a la hora de escoger tanto las estructuras hardware más adecuadas como los métodos que sacan un mayor provecho de los recursos del dispositivo. El paralelismo varía enormemente de nivel a nivel y una aplicación específica puede utilizar un grado de paralelismo intermedio, dependiendo de los costos (en términos de CLBs) y el rendimiento deseado, así por ejemplo si la velocidad de un PE es baja, este problema puede ser superado con la utilización de dos o más PEs trabajando en paralelo. Los niveles de paralelismo más destacados son los siguientes.

- **2.2.1 Paralelismo de capa.** En redes de múltiples capas, éstas pueden ser procesadas en paralelo, para lo cual se utiliza un único PE por capa, el paralelismo a este nivel es por lo general bajo, y por consiguiente de limitado valor, pero puede sacar provecho de técnicas como *pipelining*.

- **2.2.2 Paralelismo de nodo.** Éste es el nivel que corresponde a neuronas individuales, utiliza un PE para cada neurona, su implementación puede no ser posible para aplicaciones que requieran un elevado número de ellas.

- **2.2.3 Paralelismo de sinapsis.** Es el paralelismo de más alto nivel alcanzado en redes neuronales. Tiene como característica utilizar para cada neurona, elementos de proceso dotados con capacidad de cómputo paralelo, cualidad que poseen por el hecho de utilizar un número de multiplicadores igual al número de entradas en la neurona. Las aplicaciones realizadas a este nivel son muy potentes, pero así mismo el gasto de recursos es enorme.

\_

<sup>&</sup>lt;sup>29</sup> AMOS, R y OMONDI, Jagath C. Rajapakse, FPGA Implementations of Neural Networks. Holanda: Springer, 2006. p. 12.

**2.2.4 Paralelismo sistémico.** Es un paralelismo de nivel medio y resulta conveniente cuando los recursos disponibles son pocos. Consiste en múltiples procesadores trabajando concurrentemente para determinar la respuesta general de la red; es decir, cada capa se computa con paralelismo a nivel de nodo, pero las diferentes capas del sistema son evaluadas en tiempos diferentes. Esto involucra la utilización de módulos de almacenamiento para guardar datos intermedios. Las máquinas *SIMD* son ejemplo de este tipo de paralelismo.

## 2.3 ARITMÉTICA EN REDES NEURONALES

Para realizar implementaciones hardware de redes neuronales, se deben considerar aspectos referentes a la aritmética interna del diseño, estos incluyen la representación de datos, la forma en cómo se llevan a cabo las multiplicaciones y sumas de productos y la implementación de las funciones de activación.

**2.3.1 Representación de datos.** La forma de representar los datos, es un aspecto en el cual se debe tener mucho cuidado, y preferiblemente debe ser definido en las primeras etapas de un proyecto. La decisión de escoger la representación en punto fijo o en punto flotante, como más conveniente en una determinada aplicación, en general se puede tomar asumiendo que las implementaciones en punto fijo alcanzan mas velocidad y gastan menos recursos hardware, pero las precisiones que manejan son menores, mientras que en punto flotante pueden alcanzar un rango dinámico más alto y por lo tanto mayor precisión (lo cual es atractivo si se quieren utilizar algoritmos complicados) pero gastan muchos más recursos en el dispositivo. Ambos sistemas han sido estandarizados, pero pueden ser modificados a conveniencia del diseñador, para una aplicación específica. La figura 12, muestra los sistemas de representación de datos mas utilizados (...)<sup>30</sup>.

Figura 12. Sistemas de representación de datos.

<sup>&</sup>lt;sup>30</sup> FLOYD Tomas L. Fundamentos de Sistemas Digitales. 7<sup>ma</sup> ed. Madrid: Prentice Hall, 2002.

**2.3.1.1 Mínimo rango de precisión permitido**<sup>31</sup>. Un diseño en FPGA debe realizarse en forma tal, que haga uso lo más eficientemente posible de los recursos hardware que posee el dispositivo. En términos de un óptimo balance entre rango de precisión y área utilizada, esto puede ser logrado determinando *la mínima precisión permitida* y *el mínimo rango permitido*, para los cuales el criterio es minimizar el área hardware utilizada, sin sacrificar calidad de rendimiento. Esos dos conceptos combinados son referidos como el *mínimo rango de precisión permitido*.

Determinar el mínimo rango de precisión permitido puede traducirse a hallar la máxima cantidad de incertidumbre (error de cuantización debido a limitada precisión), que una determinada aplicación puede resistir antes de que su rendimiento comience a degradarse.

Hay estudios que establecen 8 bits para salidas de funciones de activación y 16 bits para pesos<sup>32</sup>. Sabiendo esto, el aspecto crítico es determinar cuándo menor precisión debe ser utilizada debido a consideraciones de rendimiento y costo. En este caso un cuidadoso análisis debe ser realizado. Debe tenerse en cuenta que gracias a las ventajas de los FPGAs y del diseño VHDL éste es un parámetro que fácilmente puede ser modificado hasta encontrar la mejor implementación.

2.3.2 Procesamiento de suma de productos<sup>33</sup>. Todas las señales que entran a una neurona artificial son multiplicadas por sus respectivos pesos y posteriormente todos estos productos son sumados en el cuerpo de la neurona. Este proceso requiere el uso de bloques aritméticos que pueden ser dispuestos de diferentes maneras dentro del diseño, entre estas disposiciones se destacan la configuración en cadena, configuración en árbol y mediante unidades de multiplicación y acumulación (MAC), la escogencia de una u otra puede variar el grado de paralelismo deseado; esto se puede observar en la figura 13.

<sup>&</sup>lt;sup>31</sup> AMOS, R y OMONDI. Op. cit., p. 40.

<sup>&</sup>lt;sup>32</sup> HOLT, J. L. and HWANG, J. N. Finite-precision error analysis of neural network hardware implementations. Washington, DC, USA: IEEE Transactions on Computers. 1993. p 290.

<sup>&</sup>lt;sup>33</sup> AMOS, R y OMONDI. Op. cit., p. 17.

Figura 13. Configuraciones habituales para suma de productos.

Fuente. FPGA implementations of neural networks.

**2.3.3 Funciones de activación.** Son usadas para determinar la salida de una neurona, tomando como argumento de entrada, la *suma de productos internos*, hay muchos tipos de estas funciones entre las cuales se destacan, sigmoidea, hard limit y purelin.

Muchas técnicas existen para evaluar estas funciones, entre las que se citan Algoritmos CORDIC, Aproximaciones Polinómicas, Expansión en Series de Taylor y Métodos por Manejo de Tablas. En términos de rendimiento precisión y costo, todos tienen ventajas y desventajas. Se quiere destacar entre estos el método por manejo de tablas, el cual optimiza la implementación de estas funciones mediante el uso de tablas internas LUTs, lo cual resulta muy conveniente teniendo en cuenta que los FPGAs vienen equipados con una gran capacidad de memoria.

**2.3.3.1 Método por manejo de tablas**<sup>34</sup>. Debido a que es necesario usar valores con limitada precisión se hace necesario discretizar tres grupos diferentes de variables, entradas y salidas de neuronas (ambas con el mismo número de bits), pesos sinápticos y el argumento de entrada de la función de transferencia. Cada uno de estos grupos tiene diferentes rangos especificados por el número de bits de la variable discreta y del máximo valor absoluto de la correspondiente variable continua.

En implementaciones digitales, únicamente la función hard limit puede ser exactamente evaluada, las demás como es el caso de las funciones purelin y sigmoidea tienen que ser aproximadas.

<sup>&</sup>lt;sup>34</sup> Ibíd., p. 280.

A continuación se describe como obtener los datos que se guardaran en la LUT para la función de activación sigmoidea y la manera de usarlos para obtener la salida de la neurona.

Con el propósito de lograr generalidad, una función de activación sigmoidea tansig(k) es definida dependiendo de tres parámetros,  $f_0$ ' (derivada en k=0),  $f_{max}$  (valor máximo de tansig(k)), y  $f_{min}$  (valor minimo de tansig(k)). Por simplicidad se define  $f_R$  como  $f_{max}$ - $f_{min}$ .

$$Tansig(k) = \frac{f_R}{1+e^{-\frac{4f_R^f}{f_R}k}} + f_{min}$$

$$f_0'=1/2$$

,  $f_{max}=1$ ,  $f_{min}=-1$

Ahora se definen algunos parámetros adicionales:

- n: máximo número de entradas a una neurona (incluye el Bias).

- M<sub>z</sub>: máximo valor absoluto de las entradas y salidas continúas de la red.

- $\triangleright$   $p_z$ : número de bits de las salidas y entradas discretas de la red.

- M<sub>w</sub>: máximo valor absoluto de los pesos continuos.

- $\triangleright$  p<sub>w</sub> número de bits de los pesos discretos.

- ➤ M<sub>s</sub>: máximo valor absoluto de la suma de productos continúa.

$$M_S = nM_ZM_W$$

N<sub>s</sub>: número de bits de la suma de productos discreta.

$$N_s = [log_2(n(2^{p_2-1}-1)(2^{p_W-1}-1))] + 1$$

### • Direccionamiento de la LUT.

Para poder acceder a los datos que contiene la LUT, el procedimiento consiste en dividir en dos partes los  $N_s$  bits que representan la suma de productos. La primera parte se compone de los  $p_s$  bits más significativos (usados como entrada de la LUT) y la segunda de los  $m_s$  bits menos significativos.

$$N_{\scriptscriptstyle S} = p_{\scriptscriptstyle S} + m_{\scriptscriptstyle S}$$

$1 \le p_{\scriptscriptstyle S} \le N_{\scriptscriptstyle S}$

Entre más grande sea  $p_s$ , más exacta es la función de activación; se debe encontrar un valor para  $p_s$  (el cual se nombrara como valor optimo  $p_{Sop}$ ), éste es el minimo  $p_s$  que satisface la condición de que todos los posibles valores de salida de la función de activación discreta están presentes en la LUT. Una posible aproximación para  $p_{Sop}$  es la siguiente.

$$p_{Sop} = \left[ log_2 \left( f_0' n M_W \frac{2^{N_S} (2^{p_Z} - 2)}{2^{N_S} - 2} \right) \right]$$

El procedimiento a realizar para hacer la discretización es el siguiente.

- $\triangleright$  El diseñador, de acuerdo a la aplicación, debe tener definidos los siguientes parámetros  $M_z$ ,  $M_w$ ,  $p_z$ , n y  $p_n$ .

- Determinar M<sub>s</sub> y N<sub>s</sub>.

- Obtener el valor óptimo de p<sub>s</sub> y m<sub>s</sub>.

- Find Indian High High Enrichment Fig. En lugar de utilizar todos los  $N_s$  bits como índices para acceder a los datos guardados en la LUT, sólo se utilizan los  $p_s$  más significativos, por tanto la LUT debe tener  $2^{ps}$ -1 datos, cada una guardando un valor entre  $M_s$  y  $-M_s$ .

Este método puede modificarse, para lograr mayor precisión, por ejemplo utilizando adicionalmente LUTs más pequeñas en los intervalos donde el error puede llegar a ser crítico, esto se acostumbra en los intervalos intermedios de la función de activación sigmoidea.

2.3.3.2 Método por aproximaciones polinómicas. Es un método muy interesante para implementar las funciones de activación de una red neuronal, consiste en combinar polinomios de bajo nivel con pequeñas LUTs. Debido a que, además de grandes capacidades en memoria los FPGAs vienen equipados con munchas unidades aritméticas dedicados (tales como multiplicadores y sumadores) resulta ser una técnica que aprovecha muy bien los recursos. Por otra parte, la interpolación a bajo nivel tiene como ventajas que las mismas estructuras pueden ser usadas para realizar diversas funciones, puesto que lo único que se debe cambiar son los coeficientes polinómicos.

Otro de los aspectos a tener en cuenta en la implementación hardware de redes neuronales es la manera en cómo se lleva a cabo el entrenamiento de la red. Éste implica cálculos aritméticos de elevada complejidad que obligan al empleo de estructuras muy sofisticadas. Éste aspecto, como se ve a continuación en la sección 2.4, puede ser manejado con mucha flexibilidad dentro de un diseño.

### 2.4 MODOS DE ENTRENAMIENTO DE UNA RED NEURONAL EN FPGA

Este término no debe ser confundido con el tipo de entrenamiento utilizado en redes neuronales (supervisado y no supervisado). Los modos de entrenamiento de una red neuronal están relacionados directamente con el lugar físico donde se lleva a cabo el aprendizaje de la misma. Se puede encontrar dos modos de entrenamiento.

2.4.1 Entrenamiento externo (offline learning). El algoritmo de entrenamiento es un proceso iterativo y como tal puede ser implementado en sistemas secuenciales, tales como las actuales plataformas computacionales (sin que con ello se vea perjudicado el procesamiento en modo de recuerdo) acorde con lo anterior, el aprendizaje de la red en este modo de entrenamiento tiene lugar fuera del FPGA. Cabe destacar que el entrenamiento es un procedimiento que se lleva a cabo hasta obtener los pesos adecuados y posteriormente se desconecta para colocar a la red en modo de recuerdo.

La implementación de este modo de entrenamiento se incluye dentro de las llamadas metodologías de Codiseño Software / Hardware, y posee ventajas que se ven traducidas en ahorro de recursos hardware (CLBs del FPGA) y en flexibilidad, gracias a que se pueden aprovechar todas las ventajas que traen consigo paquetes computacionales especializados en RNA tales como Matlab.

**2.4.2 Entrenamiento interno (on-chip learning).** Ocurre cuando el algoritmo de aprendizaje es implementado sobre el mismo FPGA. Permite que el sistema sea independiente de cualquier otro sistema digital, pero gasta una cantidad elevada de recursos respecto a sistemas que funcionan con entrenamiento externo.

### 2.5 BLOQUES BÁSICOS DE UNA RED NEURONAL

Para realizar digitalmente la implementación de una red neuronal en un FPGA se debe primeramente definir una estructura electrónica conformada por un conjunto de bloques básicos que adecuadamente ensamblados conformen el diseño electrónico.

Ocho son los bloques fundamentales que se plantean para la realización de una RNA en un FPGA. los cuales son detallados a continuación.

- 1. Módulos de Entrada.

- 2. Unidad de Cómputo Paralelo.

- 3. Interfaz.

- 4. Bloque Algorítmico.

- 5. Sistema de Comunicaciones.

- 6. Unidad de Almacenamiento.

- 7. Módulos de Salida.

- 8. Unidad de Control.

- **2.5.1 Módulos de entrada.** Es el encargado de recibir los datos desde el exterior de la red, ya sea desde un arreglo sensorial u otro sistema digital, dependiendo de la naturaleza de la aplicación. Lo ideal para su realización es utilizar estructuras para el traspaso de datos a alta velocidad como por ejemplo el puerto USB pero también pueden utilizarse otras como el puerto paralelo o el puerto RS-232.